Seamless Generation of Design, Verification, and Documentation: Elevate Your Semiconductor Development with UVM Testbench, PSS, IP-XACT, SystemRDL, and PSS Compiler Integration.

Discover the iDesignSpec™ Suite, a market-leading solution that offers extensive capabilities to ensure the correctness of every semiconductor element from the start. With our platform, you can effortlessly generate these critical components directly from your executable specifications, saving valuable time and resources.

The IC Designer’s Guide to Automated Specification of Design, Verification, and Validation for Better Products

There are multiple causes for designs being wrong, but some of the most common are related to the design specifications and how they are distributed and maintained throughout the product development lifecycle. Learn how to address this issue by reading this guide.

Transform IP/ FPGA / SoC Development with Agnisys IDesignSpec Suite

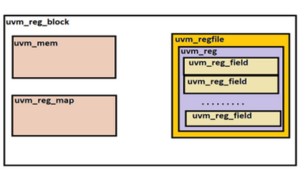

Streamline your project with automatic generation of RTL, UVM Register Layer, UVM Model, UVM Testbench for IP SOC Verification, System level SoC Validation, and IP Integration. Our suite automates file generation, benefiting designers, verification engineers, embedded programmers, pre-silicon validation engineers, and post-silicon lab teams. All files, including the programmer's manual documentation, are automatically generated, replacing manual coding and updates. Accelerate project schedules and optimize human resources with our comprehensive solution.