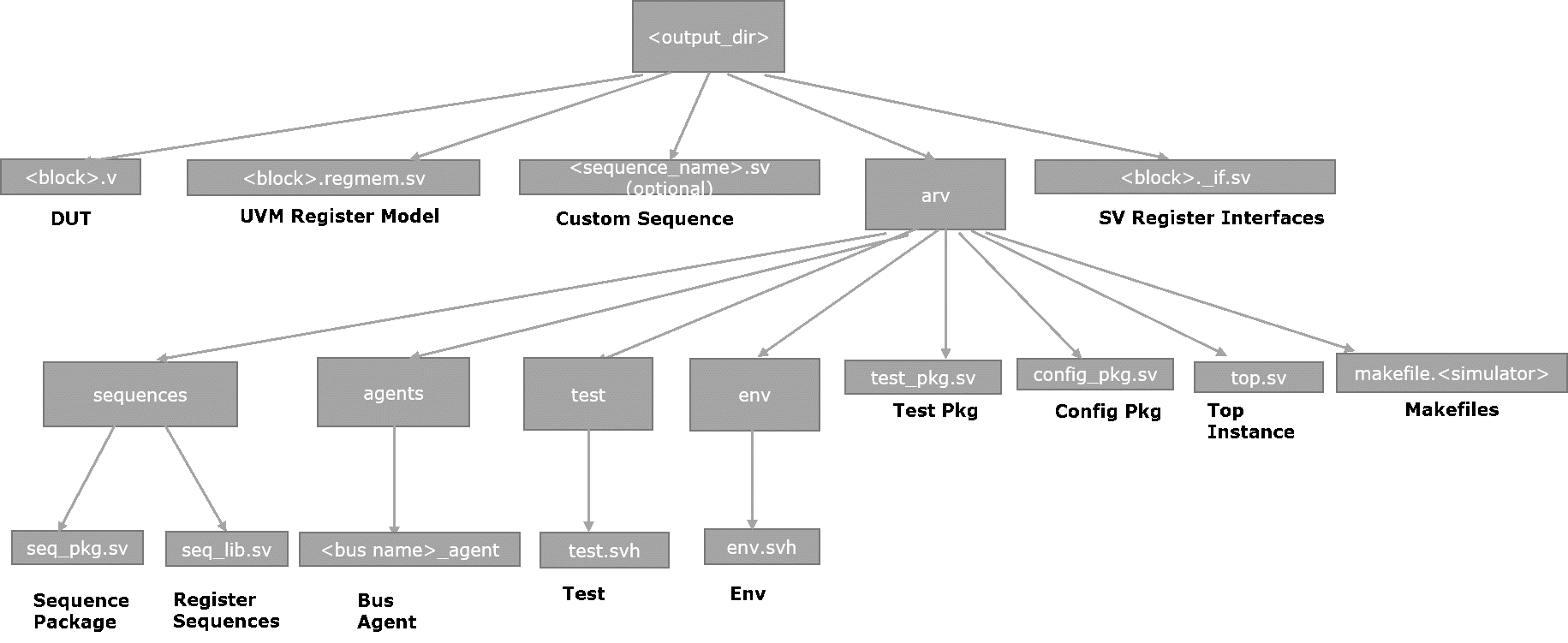

Modern RTL design verification (DV) environments are both compelling and very complex. They include advanced simulation testbenches plus support for formal verification, virtual prototypes, and emulation technology. Even within just the testbench, there is a great deal of highly sophisticated code to be written. Part of the power and complexity comes from the capabilities of the testbench. Constrained-random stimulus generation lies at the core, involving automated tests that exercise various parts of the design while adhering to the rules for input sequences. Important testbench components include interfaces, register models, bus agents, reused verification IP (VIP), results checkers, and coverage monitors. Clearly, a lot of effort is needed to create and maintain this infrastructure. A typical infrastructure is shown in the following diagram:

Although other languages are sometimes used for specific tasks or for legacy reasons, SystemVerilog is the dominant choice for writing the testbench. SystemVerilog is itself a powerful and complex language, as is the Universal Verification Methodology (UVM) standard that guides the testbench structure. Between SystemVerilog and UVM, there are literally thousands of syntactic and semantic details. It's unrealistic to expect DV engineers to memorize all these and construct a full-featured testbench from a blank screen in a simple text editor. They need a SystemVerilog- and UVM-aware tool that can provide guidance and checks at every step to yield a correct-by-construction testbench.

DVinsight from Agnisys is a smart editor for the creation of UVM-based testbenches. It checks and provides helpful insight into user code and ensures compliance with UVM best practices while adhering to established standards. It accelerates the learning curve of new DV engineers while fostering error-free code development by expert DV developers. The many capabilities of DVinsight start with a range of smart editing features.

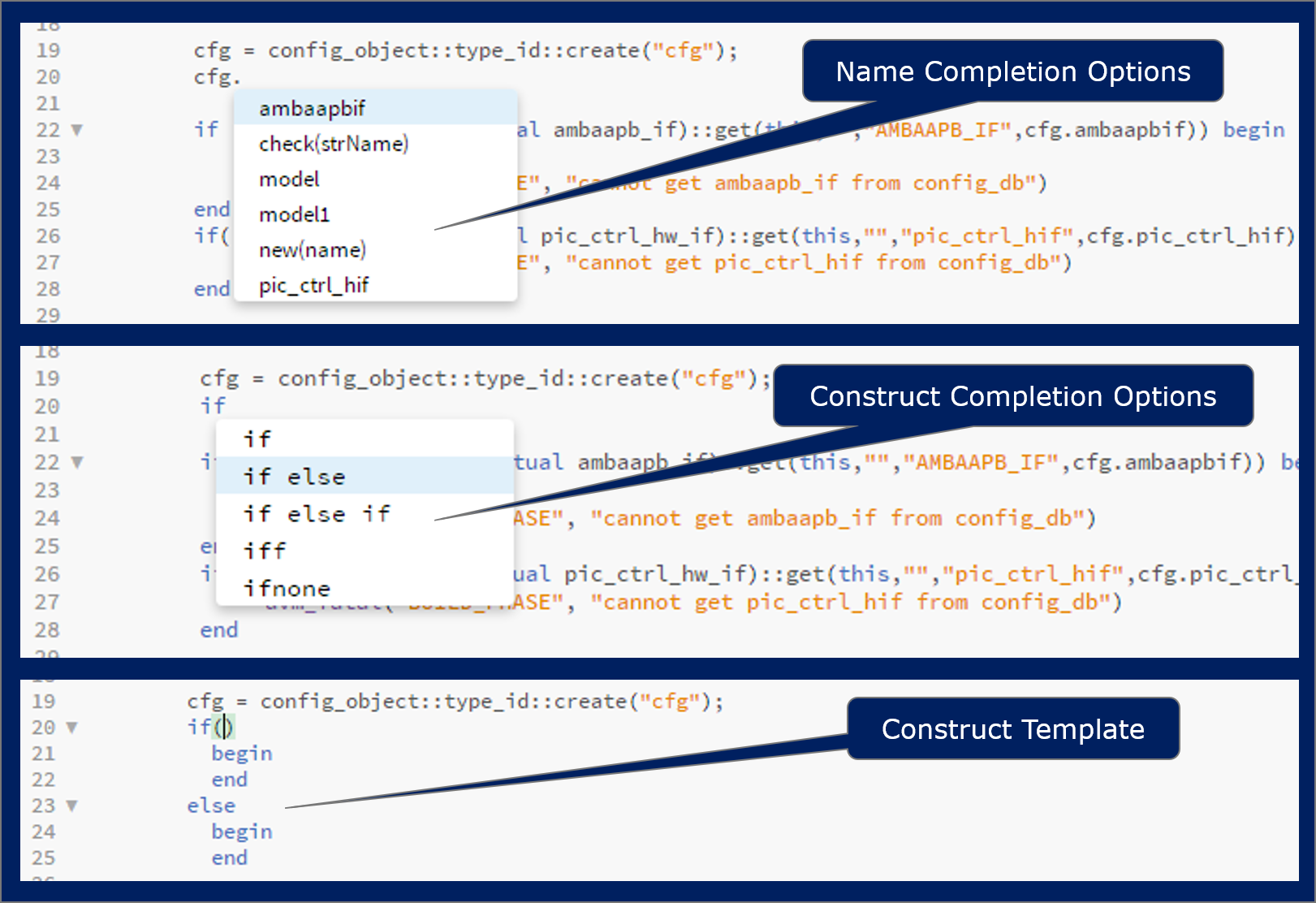

The creation of new code is made much easier by context-sensitive hints and user guidance. The tool provides templates to the user and performs automatic code completion whenever possible. If the user starts typing the name of a variable or testbench component, the tool will display all the available options in a pop-up menu for easy selection. The same process applies when the user types part of a language construct; the tool provides a menu of code hints. When the user makes a selection, the tool automatically generates a template to be filled in. For example, selecting an “if” construct generates the “if() … begin … end” template, while selecting “if else” creates the “if() … begin … end … else … begin … end” template.

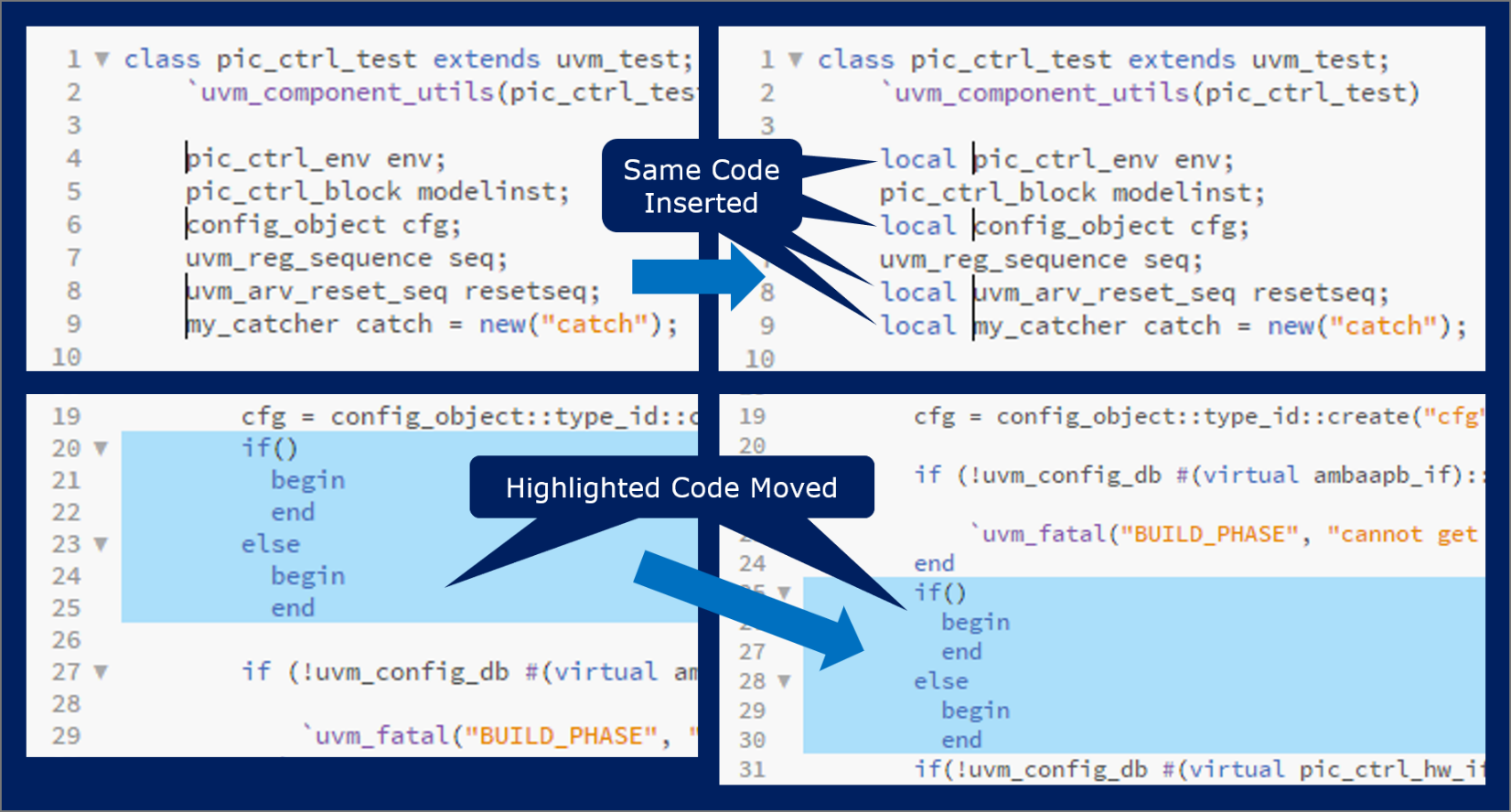

The smart editing features extend well beyond writing new code to cover navigating and editing existing code. The user can edit multiple files quickly by opening them in multiple split windows. DVinsight can compare two versions of a file and show the differences side by side. The user can open an “insight” of files within the same editor window. For example, using the “Ctrl + E” shortcut on an instance of a class will open the file with the class definition for editing. Any changes made to the class, such as adding a method, will be visible in the pop-up windows back in the original file.

Multiple lines in a file can be edited together within a single context. The user can place multiple cursors on multiple lines, and then type in the common code to be inserted at the cursor point in each line. You can easily move blocks of code from one location to another without resorting to copy-and-paste commands. The user highlights the code and moves up or down in the file using the “Ctrl + Shift + Arrow” key combinations. Text searches are both quick and intelligent; all instances of the searched term are highlighted in the code and their locations are marked on the scroll bar for easy navigation.

Beyond correct syntax and semantics, proper indentation and copious comments are important aspects of creating testbench code that is understandable, maintainable, and extensible for follow-on design projects. DVinsight provides handy keyboard shortcuts to make both of these tasks easier. The currently selected line, multiple lines, or block of lines is indented right with each “Ctrl + [” and left with each “Ctrl + ]” shortcut. The user can start a single-line comment at the current location with “Ctrl + /” and a multi-line comment with the “Ctrl + Shift + /” combination. When it comes to shortcuts, many users have years of experience with the Vim (based on vi) text editor or the Emacs text editor. They can use their familiar key bindings within DVinsight.

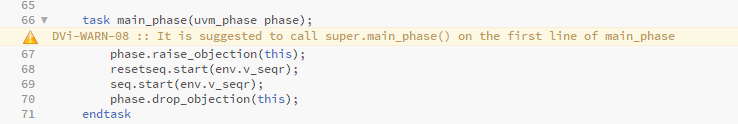

In addition to its code editing features, DVinsight helps ensure that the testbench code is correct before being sent to the simulator. Syntax errors are detected “on the fly” as the user types in the code. A built-in UVM linter performs an extensive series of checks every time the code is saved. These checks go beyond just syntax and semantics to ensure that the testbench conforms to UVM best practices. This has several big advantages:

- Helps in creating DV testbench code that is correct by construction

- Catches SystemVerilog and UVM errors early in the process for quick fixes

- Minimizes long debug loops through simulation compilation and error detection

- Eliminates consumption of simulator licenses just to detect testbench coding errors

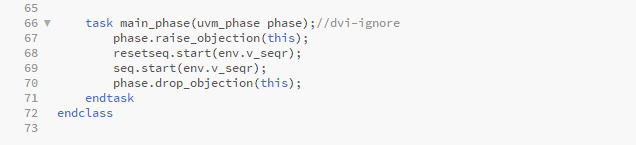

The user can selectively choose to ignore the warnings flagged by DVinsight by inserting a single-line comment with the keyword “DVI-ignore” at the first line of the enclosing scope. For example, if it is mentioned on the line where a class is defined then it is applied to the whole class. If it is on the line where a function/task is defined then it is applicable within the function/task.

When the code is clean enough to try compiling, DVinsight links directly to popular simulation platforms. The user can open a console window to type commands to the shell and invoke the simulator. Any compilation errors detected are cross-referenced in DVinsight. The user can click and open file names with errors and then move back and forth between the editor and the simulator. This greatly reduces debug time and enables the resolution of compilation errors in the context of the testbench source code and with interactive navigation and editing features.

DVinsight accelerates error-free DV code development and reduces the learning curve for SystemVerilog and UVM. It ensures compliance with UVM best practices and established standards while shortening debug time and optimizing simulator license usage. Best of all, a free version is available for download. Details on a premium version named DVinsight-Pro can be found here. For more information on DVinsight, a webinar is available as part of an extensive series covering a broad range of design and verification topics. DV engineers can register here at their convenience.