Navigating SoC Complexity

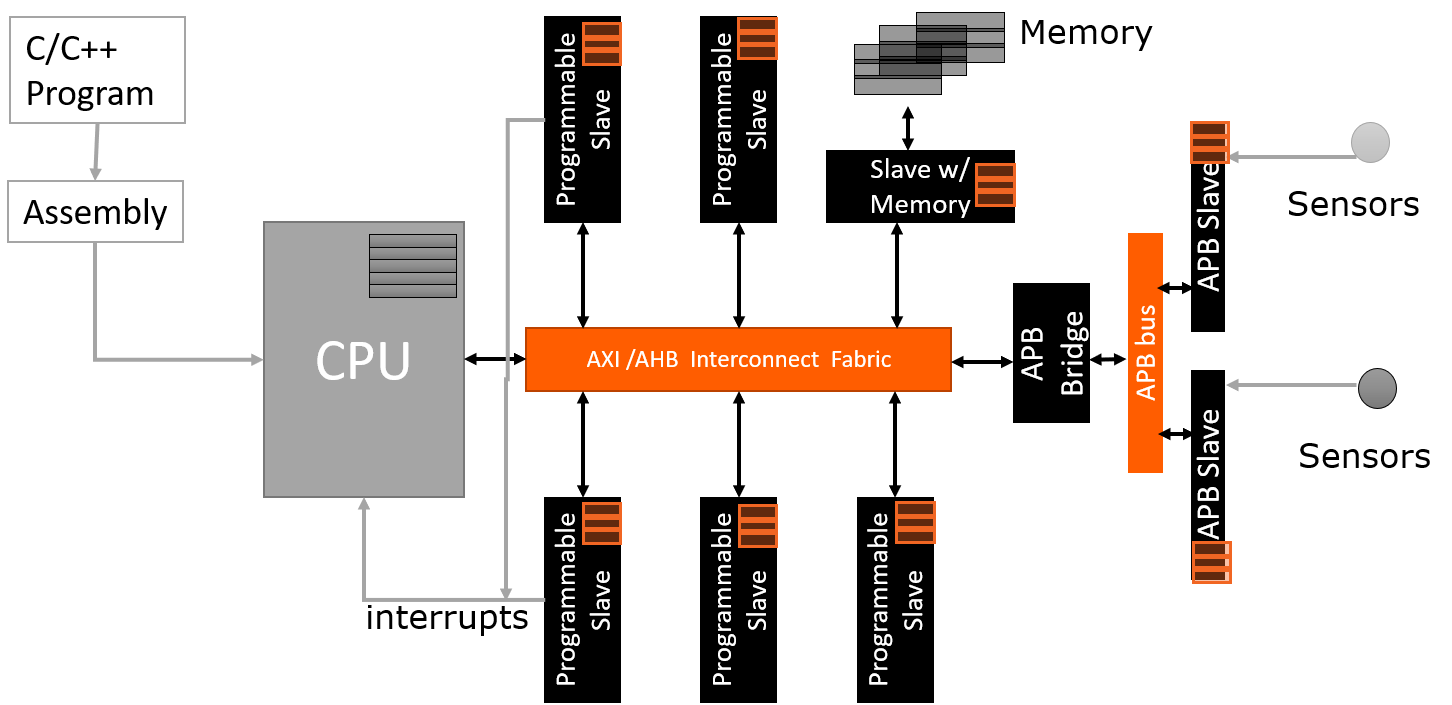

System-on-chip (SoC) projects are, by their very nature, complex and difficult to complete successfully. Specification, architecture, design, and verification are all challenging. The blog addresses challenges for designers arising from applications converging onto a single SoC device, emphasizing their impact and solutions. This increases the demand for design functionality and design performance. At the same time, market requirements generate pressure to drive down the cost of design and meet shrinking market windows due to shorter product shelf lives. Every step of the design process has become more difficult, even the seemingly simple task of assembling all the pieces that make up the SoC.

Today’s large chips may contain 500 or more instances of intellectual property (IP), a combination of new designs, reused blocks from previous projects, and licensed commercial IP. If each of these blocks averages 50 ports, then 25,000 connections must be made among them. Making these connections manually is tedious and time-consuming, with a high chance of errors. Meeting cost and schedule goals requires a big increase in the productivity of the SoC design team. Methodology improvements are needed to help accelerate the assembly of chips and systems through automation.

The best solution involves offering designers adaptable IP and subsystem generators, coupled with a tool for automating architectural-level SoC assembly and connectivity. The capabilities for such a solution include:

- Creating and editing the design on the fly through scripts or a command-line interface

- Generating major subsystems with the flexibility to customize or configure

- Automatically adding instances to the design, making connections, restructuring, etc.

- Viewing the resulting schematics for design analysis

- Running design rule checks to endure IP and SoC quality

- Generating appropriate files for design, verification, and software teams

Streamlining SoC Design with Customizable IP Assembly and Smart Integration

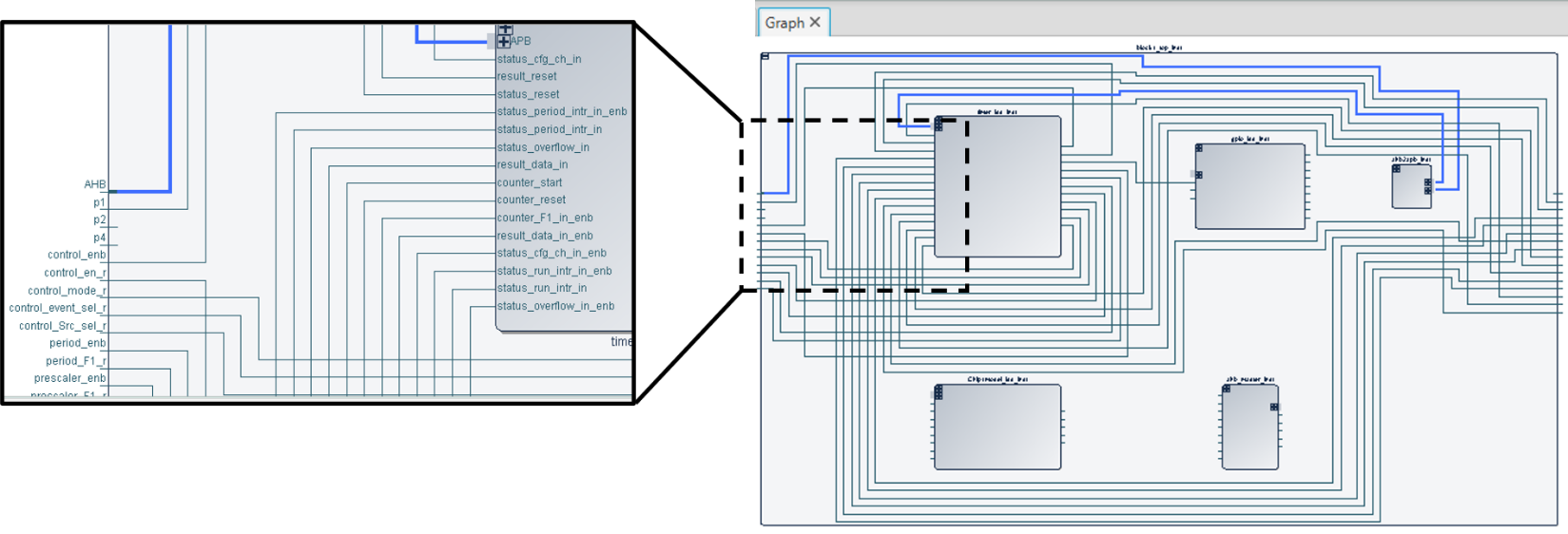

As introduced in March, Agnisys IDS-Integrate™ is a flexible and customizable environment for design assembly that meets all the requirements discussed above. It helps create, package, integrate, and reuse IPs and SoCs. It is fully compliant with the IP-XACT (IEEE 1685-2014) standard used by many IP providers to document their designs. As an enterprise-level solution, it can support design teams spread around the world and integrate their IP blocks into the full SoC. It supports a command mode through text-based APIs and a GUI mode fully integrated within Agnisys IDesignSpec™ GDI.

The Agnisys solutions do more than assemble existing blocks; they can actually generate multiple forms of IP in register-transfer-level (RTL) format. Agnisys IDesignSpec™ GDI generates RTL for registers and memories based on designer specifications. The IDS-IPGen™ tool from Agnisys provides RTL generators for standard IP blocks such as GPIO, I2C Master, a timer, and a programmable interrupt controller (PIC). All of these are easily customizable and configurable to meet user requirements. IDS-Integrate automatically integrates and connects all these blocks in the SoC using its Smart Assembler technology.

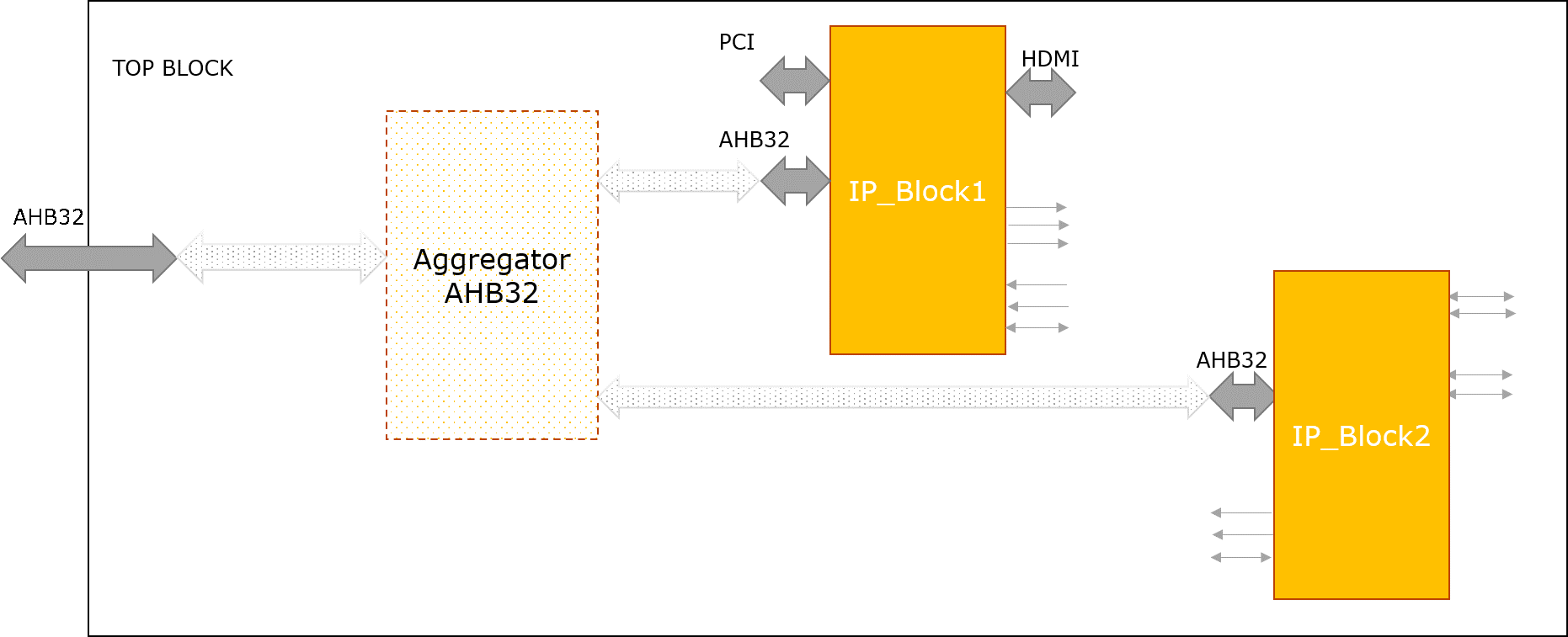

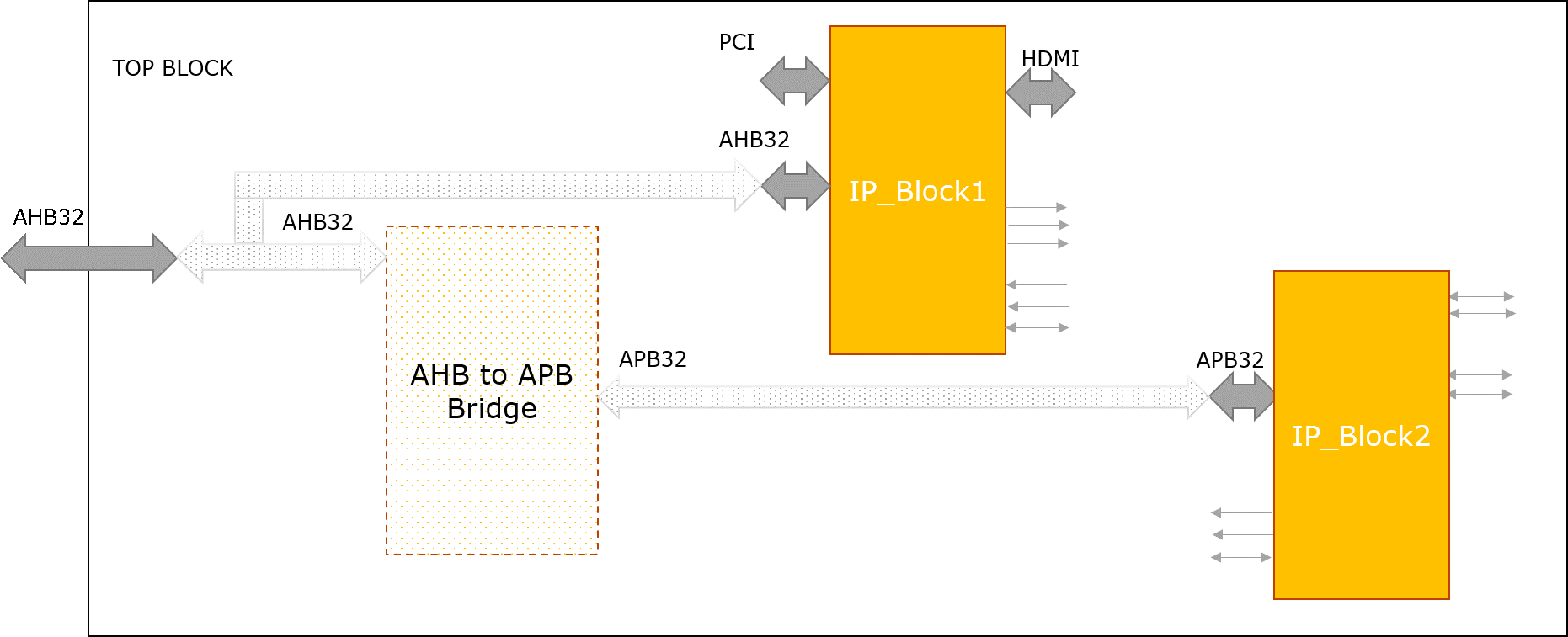

For standard buses such as AHB and APB, IDS-Integrate can generate RTL aggregators, bridges, and multiplexors as needed to meet the required architecture for the SoC. For example, the AHB interfaces on two IP blocks can be aggregated into a single bus to connect to chip pins. Similarly, if the design includes an IP block using AHB and IP blocks with APB interfaces, IDS-Integrate can automatically generate an AHB-to-APB bus bridge between the high-speed system bus and the lower-speed peripheral bus. Smart Assembler automatically integrates and connects these blocks as well.

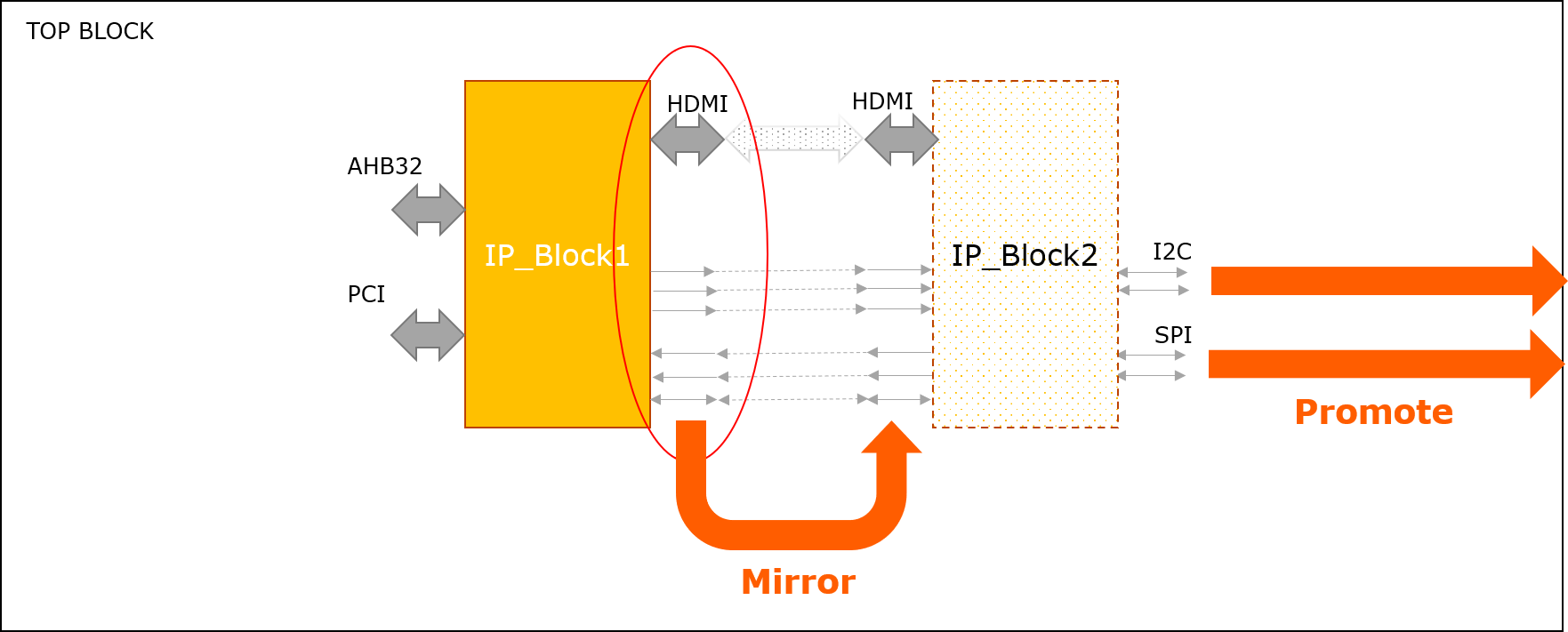

Smart Assembler can also automatically connect custom design blocks. The user can select a set of ports on a block and direct IDS-Integrate to automatically create the template for a new block with the same set of (mirrored) ports and then connect the two blocks. Smart Assembler connects existing blocks with mirrored ports and can link arbitrary blocks if the user supplies a list of connections. These capabilities provide a highly efficient way to populate the SoC with interconnected IPs even before the RTL functionality is fully specified. The user can also have IDS-Integrate “promote” selected ports to the top level so that they can become chip pins.

The size and complexity of today’s SoCs demand automation for many aspects of design and verification. Chip assembly, including the connection of design blocks, is a prime target for increased designer efficiency and faster time to market. IDS-Integrate provides an industry-leading solution. Effective IP and subsystem reuse is possible with the flexible, customizable, and configurable generators from Agnisys. IDS-Integrate also supports reuse in verification, firmware, and software by generating appropriate files for those teams. Chip development is faster, better, and less expensive with this advanced automation.

More information on IDS-Integrate and Smart Assembler is available in a webinar, part of an extensive series covering a broad range of design and verification topics. Details and registration instructions are available here.