and IP-XACT Based RAL Model, UVM Testbench/Tests, and Documentation Generation

Streamline SOC, ASIC, and FPGA Development by automatically generating development collaterals

Faster IP/SoC Design & Verification

Automated Register Generation, SoC Assembly & Packaging

The IC Designer’s Guide to Automated Specification of Design, Verification, and Validation for Better Products

There are multiple causes for designs being wrong, but some of the most common are related to the design specifications and how they are distributed and maintained throughout the product development lifecycle. Learn how to address this issue by reading this guide.

The IC Designer’s Guide to Automated Specification of Design, Verification, and Validation for Better Products

There are multiple causes for designs being wrong, but some of the most common are related to the design specifications and how they are distributed and maintained throughout the product development lifecycle. Learn how to address this issue by reading this guide.

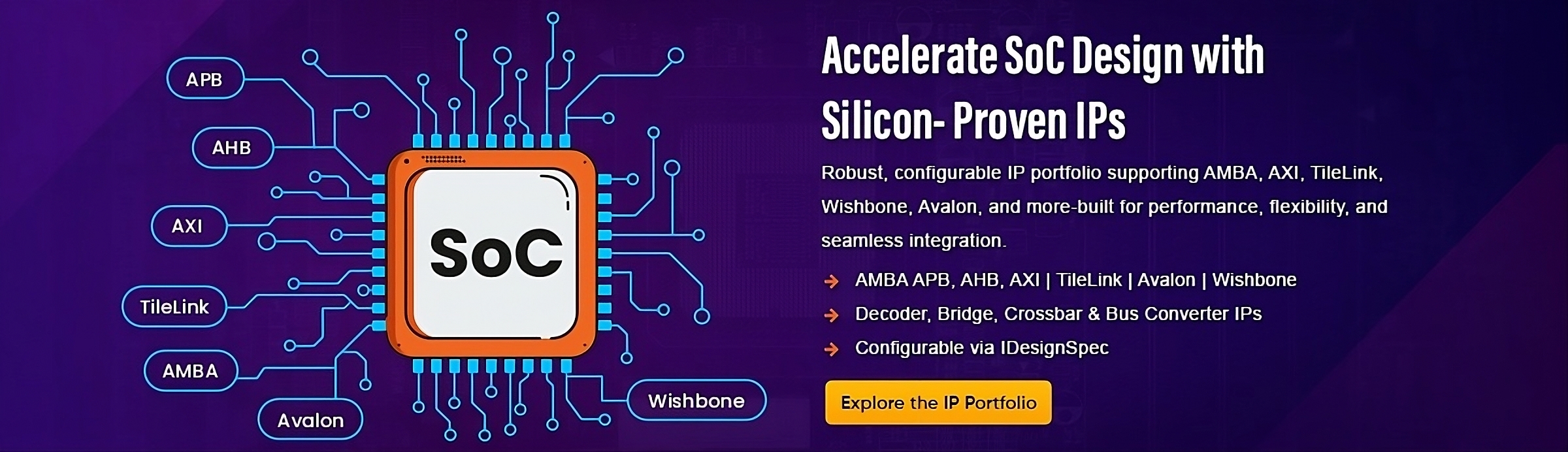

How the IDesignSpec benefits various application areas

Design |

Automate RTL generation for registers, memories, CDC logic, DFT, and IP connectivity—ensuring correctness and scalability from day one. |

Verification |

Generate UVM RAL models, testbenches, assertions, and AI-powered tests to accelerate coverage closure and reduce verification cycles. |

Validation |

Enable faster system validation by generating C/C++ test cases, bare-metal software environments, and UVM-C–based validation flows from the same executable specification. |

Software |

Automatically generate C/C++ headers and memory maps from the same specification—eliminating manual translation and mismatches. |

Tech Pubs |

Produce always-up-to-date HTML, PDF, and Word documentation directly from the executable specification, with URL-based sharing via IDS-CF. |

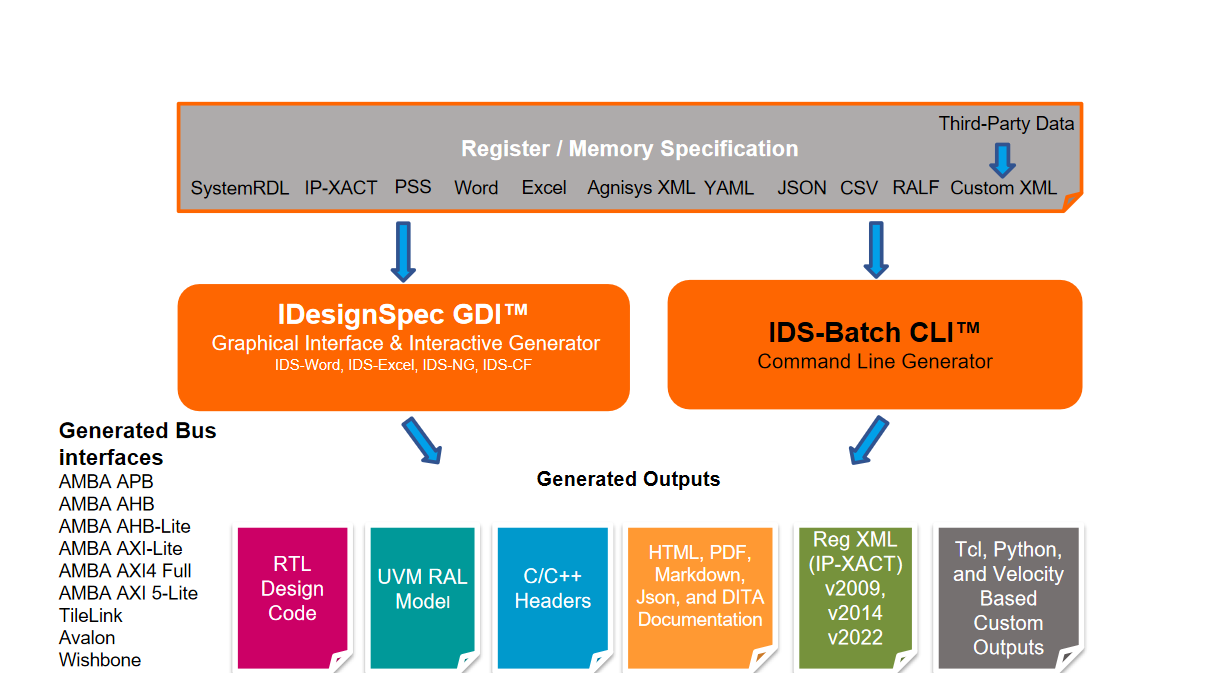

Transform IP/ FPGA / SoC Development with Agnisys IDesignSpec Suite

Streamline your project with automatic generation of RTL, UVM Register Layer, UVM Model, UVM Testbench for IP SOC Verification, System level SoC Validation, and IP Integration. Our suite automates file generation, benefiting designers, verification engineers, embedded programmers, pre-silicon validation engineers, and post-silicon lab teams. All files, including the programmer’s manual documentation, are automatically generated, replacing manual coding and updates. Accelerate project schedules and optimize human resources with our comprehensive solution.

Products that Streamline Semiconductor

Development

The Agnisys IDS suite delivers end-to-end automation for semiconductor design, verification, validation, and integration. Built around a unified GDI, generation engine, and Collaboration Framework, IDS enables teams to work from a single executable specification to generate consistent, production-ready outputs across the entire development flow.

What Our Customers Say

Agnisys: Automating Innovation in Semiconductor Design

Agnisys delivers cutting-edge tools that automate the most complex stages of chip development—from IP to SoC. Our intelligent design automation solutions help semiconductor teams reduce risk, cut development time, and achieve first-time-right silicon. See how Agnisys is powering smarter, faster hardware design across the globe.

Recent Blog Posts and News