5 Ways Register Generation Tools Reduce SV/UVM Implementation Time

Modern SoCs get more and more complicated every day. As the complexity of modern electronic semiconductor device design increases, niche tools for every nook and cranny of the design process emerge to help semiconductor companies keep pace with their emerging challenge. Register and memory map definition and code generation is one example of a niche tool that has become mainstream.

The reason why these register generation tools have been adopted and the rate of adoption is increasing is because there are so many benefits of doing so. There are few opportunities where a single tool can provide benefits to multiple groups. Project leaders should consider embracing a modern register and memory map generation tool to keep up with the complexities of design, verification, and embedded coding.

These 5 ways are just the start of why it makes sense to adopt register generation tools:

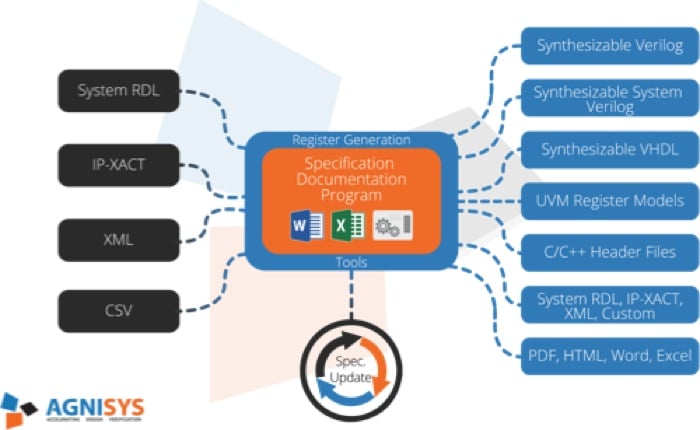

- These tools start with a simple input format specification created by the architect or senior design engineers. The tool takes that specification and expands it to provide multiple teams with functionally correct, synthesizable RTL code, UVM verification code, C-Header files, and documentation.

- One group that is always under the gun is the Design Verification team. Upon completing the specification, the DV team utilizes the generated code to expedite the creation of the UVM register abstraction model. Doing it this way provides the design verification team with instant access to an up-to-date RTL model and updated test-bench-related code. The DV team is no longer working with an old design code that is out of date or discovers at a later time that changes in the design were not reflected in the testbench resulting in bugs or incomplete tests.

- These tools provide functionality not available in old or technology-specific formats such as SystemRDL, IP-XACT, or simple spreadsheet methods. These tools take the specification and produce complete and robust code for each stakeholder. Additionally, the tools are configurable to enable the customization of target outputs that may be specific to your company.

- Tools like this enable fast turn-around times, allowing multiple iterations per day. Issues discovered during design verification that require a specification change commonly drive these iterations. Tools like these, enable the resulting specification change to immediately propagate to each group that is a consumer of the impacted code change.

- Testing these tools against numerous designs ensures that the generated code is both syntactically and semantically correct.

The bottom line about register generation tools and SV/UVM implementation time:

By adopting an automatic code generation tool for registers and memory maps from specifications, semiconductor design teams gain significant productivity benefits, and reduce the risk of complex designs while removing multiple error sources that emerge as design specifications change.