IDesignSpecTM GDI Next Generation Semiconductor Specification Automation

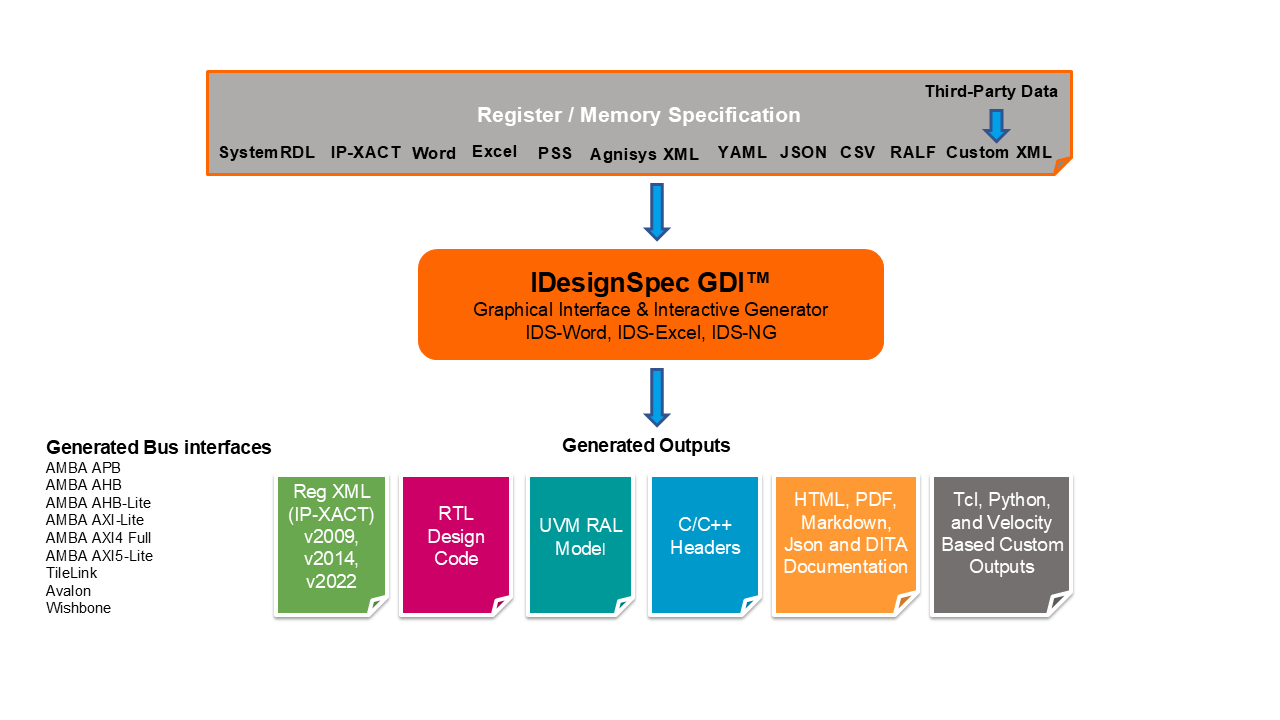

Agnisys IDesignSpec GDI (Graphical Design Interface) provides a complete solution for executable hierarchical specification of your memories, register sets, registers, and register fields in an IP or SoC. You can choose from a variety of input formats. You can import existing descriptions in standard formats such as SystemRDL, IP-XACT, JSON, RALF, YAML, XML, and comma-separated values (CSV) files for generation of various RTL, UVM, C/C++ Header, documentation collartals, etc.

Powerful Register and Memory Editor with SystemVerilog & UVM Generation

You can specify the registers and memories using Agnisys-supplied templates and Add-ins for Microsoft Word or-Microsoft Excel.

For maximum benefit and flexibility, you can choose the highly intuitive specialized register and memory editor contained within IDesignSpec GDI, a graphical user interface (GUI) for specification entry. IDesignSpec GDI interactively generates a wide variety of output files for the teams on your project, supporting design, verification, embedded programming, validation, and documentation.

IDesignSpec GDI fits seamlessly into your SoC or IP development flow, including integration with the Git revision control system to manage both text and graphics files while fostering collaboration.

How IDesignSpec GDI Enhances Your Development Process

This executable specifications read by IDesignSpec GDI support simple registers as well as more than 400 special register types, including indirect, indexed, read-only/write-only, alias, lock, shadow, FIFO, buffer, interrupt, counter, paged, virtual, external, read/write pairs, and combinations of these types.

.

RTL generation of registers, memories, CDC logic, and advanced bus connectivity

From your specifications, IDesignSpec GDI interactively generates output files for your design, verification, software, and documentation teams. It generates the complete RTL description for the registers and memories, including a bus slave and decode logic specific to the user-selected bus protocol and any clock-domain-crossing (CDC) synchronization logic needed. This enables instant connection of your design to the registered bus. Supported interfaces include APB, AHB, AHB-Lite, AXI4, AXI5-Lite, TileLink, Avalon, Wishbone, and proprietary buses.

The generated SystemVerilog, Verilog, VHDL, or SystemC RTL code for the registers is human-readable with easy-to-follow comments. Your hardware design team simply adds the generated files to their list of hand-written application logic RTL blocks and third-party IP blocks for use with simulation, logic synthesis, and other tools in the development flow.