IDS-FPGA

From Specification to FPGA Bitstream—Faster, Smarter, and Error-Free

FPGA design engineers face ever-increasing pressure: tighter timelines, more complex systems, and growing verification demands. IDS-FPGA is built to ease that pressure. It brings automation, consistency, and speed to your FPGA design, verification, and implementation workflows, allowing you to focus on building smarter systems instead of wrestling with low-level details.

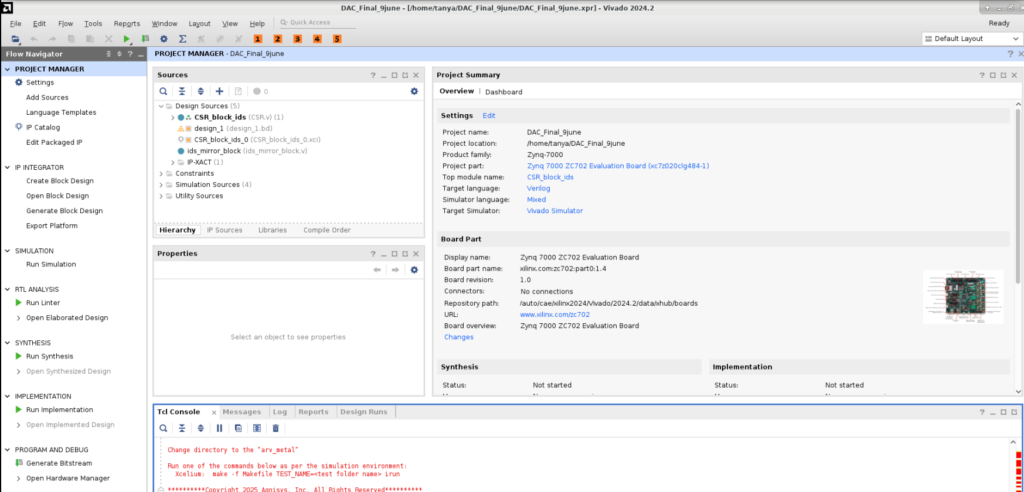

Whether you’re targeting Xilinx (AMD) Vivado or Intel (Altera) Quartus environments, IDS-FPGA plugs right into your existing flow automatically generating required CAD scripts for downstream tools.

What Can IDS-FPGA Do for You?

- Eliminate Manual RTL Coding: Automatically generate clean, synthesizable RTL from a high-level register specification.

- Cut Down Verification Setup Time: Auto-generate complete UVM testbenches—including RAL models and tests—from the same spec.

- Align Hardware and Firmware Early: Generate firmware headers and programmable sequences that ensure perfect hardware/software alignment.

Avoid Rework: Validate early, iterate faster, and go from design to lab in record time.

Key Challenges Solved

Problem FPGA Engineers Face

- Manual RTL coding: introduces errors

- Verification setup is time-consuming

- HW/SW integration lags behind

- Lack of Spec traceability and reuse

- Toolchain integration is fragmented

How IDS-FPGA Helps

- Auto-generates RTL from a GUI Specification or SystemRDL

- Auto-Generates complete UVM verification environments

- Produces firmware headers and software-accessible sequences

- Ensures 100% traceability from specification to FPGA Implementation

- Integrated Vivado and Quartus tool flow with IDS-FPGA

Core Features

- Vendor-Aware FPGA Tool Integration

Supports design flows for AMD Vivado and Intel Quartus. - Automated RTL + IP Packaging

Generates IPs with standard bus interfaces (AXI, AHB, APB, etc.). - UVM-Based Verification Generation

Builds ready-to-run UVM testbenches with integrated RAL models. - Firmware Interface Generation

Creates firmware headers and test sequences for software teams. - Spec-to-System Traceability

Maintain a single source of truth across RTL, testbench, firmware, and docs. - Customizable Config/Test Sequences

GUI-driven sequence generation for lab bring-up or simulation.

Supported Bus Interfaces

- AXI5-Lite

- AXI4-Full

- AHB-Lite

- APB

- TileLink

- Avalon

- Wishbone

Why FPGA Engineers Trust IDS-FPGA

- Speed: Shrink design cycles with high-quality auto-generated outputs

- Accuracy: Minimize bugs with first-time-right designs and pre-verified IP

- Productivity: Focus your engineering effort where it matters—innovation

- Consistency: Use a single spec to generate RTL, validation, docs, and firmware

Try IDS-FPGA Today

Join a growing community of FPGA engineers who trust IDS-FPGA to accelerate their development cycles—from IP definition to final system validation.

IDS-FPGA Latest Press Release

Agnisys showcases next-generation EDA solutions at DAC 2025, including IDesignSpec Suite v9, IDS-FPGA Launch, AI² and IDS-Integrate Enhancements.

Request a Live Solution Demonstration

From Specification to FPGA Bitstream—Faster, Smarter, and Error-Free