SOC DESIGN

SoC Design

Developing a modern system-on-chip (SoC) device is challenging in many ways, but it starts with the design. Without a design, there’s nothing to verify, program, or validate. The design begins as a register-transfer-level (RTL) description, is transformed into gates and transistors by logic synthesis and layout tools, and is ultimately fabricated in silicon.

IT all Starts with IP

IDS-IPGen: Configurable & Customizable IP Generation

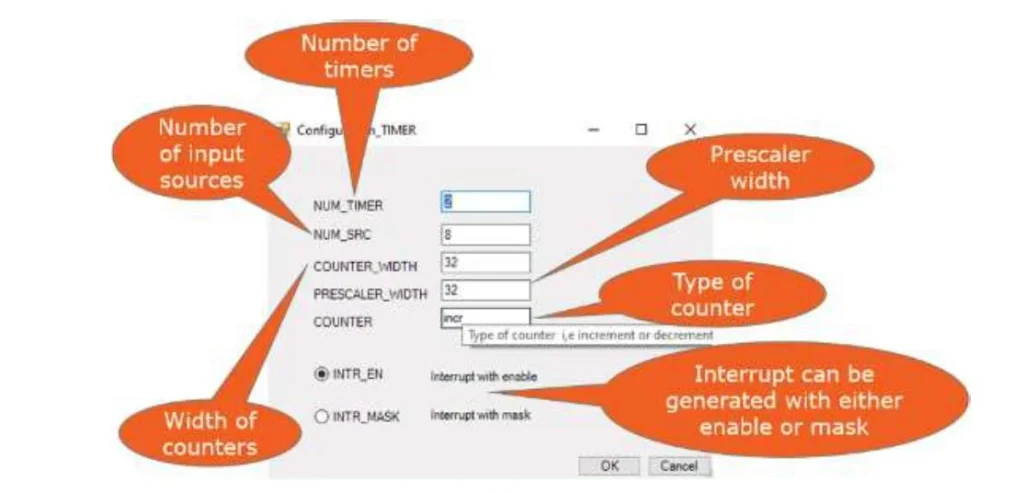

Agnisys simplifies SoC IP generation with IDS-IPGen™, part of the IDesignSpec™ Suite, enabling designers to create custom and configurable RTL IP blocks. This generative approach allows easy customization to meet specific application needs.

With IDS-IPGen, designers can tailor key attributes like bus widths, port numbers, and optional functionalities using an intuitive graphical interface. If requirements change, simply re-generate the IP with updated specifications.

Many IDS-IPGen-generated functions comply with industry standards, reducing the need for in-depth expertise. Supported IPs include AES, DMA, GPIO, I2C, I2S, PIC, PWM, SPI, Timer, and UART.

Support for Custom IP & Unique Designs

While commercial IP blocks form the foundation of many SoCs, differentiation comes from custom IP. IDS-IPGen streamlines custom finite state machine (FSM) generation, while IDesignSpec GDI and IDS-Batch CLI handle registers and memories—all in synthesizable RTL for simulation and synthesis.

Since SoCs require both hardware and software, the IDesignSpec Suite also generates UVM sequences for verification and C/C++ code for validation and software development, ensuring seamless integration across the entire design flow.

Hooking up IP Blocks Is a Pain

IDS-Integrate: Automating IP Integration for SoC Design

IDS-Integrate™ simplifies and automates the integration of IP blocks into a complete SoC. It efficiently stitches IPs using buses, interfaces, or wires, ensuring seamless connectivity across the design.

Key Capabilities

- Automated IP Hookup: Connects IPs using predefined rules, reducing manual effort.

- Intelligent Name Mapping: Matches ports with identical or similar names for hassle-free integration.

- Bus & Interface Handling: Automatically generates aggregators, bridges (AHB to APB, AXI to APB), and multiplexers as needed.

- Hierarchy Management: Restructure, flatten, or partition the design for optimal organization.

- Multi-Format Support: Works with IP-XACT, SystemRDL, RTL, and third-party IPs.

- Scripting & API Integration: Define connections using Tcl, Python, Java, or C++ APIs.

With IDS-Integrate, designers can assemble a complete SoC faster, with fewer errors, while ensuring a well-structured and scalable architecture.

Agnisys Automates SoC Design

To meet ever tighter TTM requirements for ever larger and more complex SoCs, designers can no longer write and interconnect all their RTL blocks by hand. Agnisys provides specification automation solutions that generate correct-by-construction RTL designs plus files to help with verification, validation, and software. The benefits of this automation are replicated every time that specifications change. The result is faster chip development with fewer resources and increased confidence.