Power Optimization Techniques in Digital Design: Clock Gating, Low-Power Switching, and Clock Enable

In digital design, saving power is extremely important. It’s a top priority because it helps devices run efficiently. As electronic devices become increasingly pervasive and integral to daily life, minimizing energy consumption without sacrificing performance has emerged as a critical objective. In this article, we delve into key techniques and methodologies employed by IDesignSpec™ in digital design to achieve power efficiency, with a particular focus on clock gating and low-power switching.

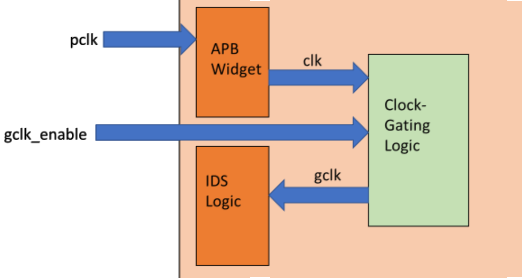

Clock gating, a widely adopted strategy in VLSI design, entails the selective activation of clock signals to logic elements only when necessary. By disabling clocks for inactive logic blocks, clock gating minimizes unnecessary switching activity and dynamic power consumption. This technique is instrumental in reducing power dissipation in modern electronic systems.

Low-power switching techniques leverage advanced circuit topologies to minimize energy dissipation during signal transitions, particularly crucial in battery-powered applications. By optimizing the design of circuit elements, such as transistors and interconnects, low-power switching mitigates power losses associated with signal transitions. Integrating these techniques into the design process requires a meticulous approach, considering factors like signal integrity, timing constraints, and area overhead. However, the benefits in terms of power efficiency are undeniable, making low-power switching indispensable in contemporary digital design.

Another pivotal aspect of power optimization is clock enable, which involves selectively enabling or disabling functional blocks based on specific criteria. This granular approach to power management allows for fine-tuned control at the module level, further enhancing energy efficiency. Properties like “-lowpower” and “power_opt” in tools such as IDesignSpec™ facilitate the integration of these techniques into the design flow, streamlining the implementation of power-optimized solutions.

IDesignSpec™, an integral part of the design process, plays a crucial role in generating low-power RTL code. By eliminating redundant assignments and minimizing write operations, IDesignSpec™ ensures that the generated code consumes low power without compromising performance. Leveraging properties like “-lowpower”, “-power_opt”, “clock_enable” IDesignSpec™ incorporates power-saving techniques seamlessly into the design flow, empowering designers to create energy-efficient solutions.

As digital devices continue to evolve, the importance of power optimization cannot be overstated. Sustainable and efficient electronic systems rely on the judicious application of power-saving techniques throughout the design process. By incorporating clock gating, low-power switching, and clock enablement strategies, designers can achieve significant power savings without compromising functionality. Moreover, as technology advances and new challenges emerge, continued innovation in power optimization will be essential to meet the demands of an increasingly energy-conscious world.

In conclusion, power optimization is not merely a technical consideration but a fundamental imperative for the development of next-generation electronic systems. Through the adoption of innovative techniques and methodologies, designers can pave the way for a more sustainable and energy-efficient future. With tools like IDesignSpec™ facilitating the integration of power-saving techniques, designers are empowered to create cutting-edge solutions that deliver both performance and energy efficiency.