IDS-Verify: The CSR Sign-off ToolTM

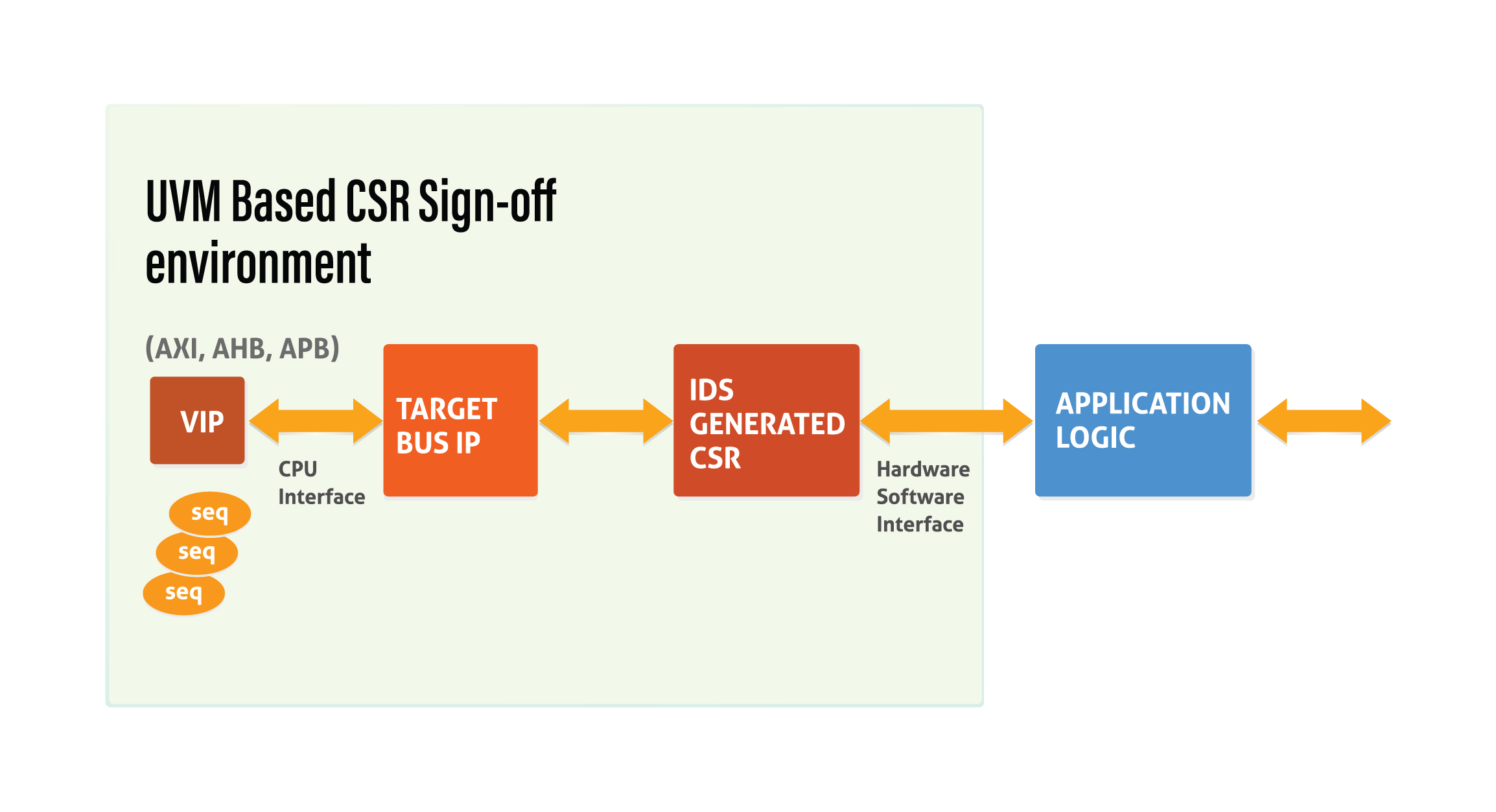

IDS-Verify is a specification-driven verification solution that enables automated control and status register (CSR), CPU peripheral and hardware–software interface (HSI) verification for modern IP and SoC designs. It converts register specifications directly into a complete, simulation-ready verification environment, including UVM testbenches, verification sequences, coverage models, and assertions, enabling teams to achieve CSR verification sign-off efficiently and consistently.

Verification teams often spend weeks or even months building testbenches, writing sequences, and iterating to meet strict 100% coverage goals for CSR, CPU peripheral and Hardware Software Interface verification. This process is highly repetitive and resource-intensive, often involving manual testbench development, custom scripts, and continuous effort to maintain alignment between specification, design, and verification. Integration challenges across IPs, tools, and teams, along with repeated verification effort for every design iteration, further increase engineering effort and delay sign-off, ultimately impacting time-to-market.

IDS-Verify eliminates this complexity by automatically generating a complete, coverage-driven CSR verification environment from the specification. It enables a plug-and-play verification flow with minimal setup, provides ready-to-run Makefiles for quick simulation execution, and ensures alignment through a single source of truth (SSOT). By accelerating coverage closure and eliminating manual effort, it frees up valuable time for engineers to focus on core design functionality, system-level scenarios, and high-value verification work, making teams more productive in less time while ensuring Hardware Software Interface correctness.

How IDS-Verify Helps Achieve 100% Coverage Closure

IDS-Verify introduces a specification-driven CSR verification flow, where the specification becomes the single source of truth.

It supports multiple input formats:

- SystemRDL, IP-XACT

- IDS-Word, IDS-Excel, IDS-NG, IDS-CF (GUI-based)

- Other formats such as XML, CSV, JSON, YAML, etc.

Additionally,

- Hand-written RTL

- Third-party IP

- Open-source designs

- AI-generated RTL

From this input, IDS-Verify enables push-button CSR verification by automatically generating:

- Complete UVM testbench for CSR, CPU peripheral, and Hardware Software Interface

- CSR verification sequences (automatic + custom)

- Functional coverage and assertions

- Protocol-aware bus verification environment

- Simulation-ready Makefiles (Questa®, Xcelium®, VCS®)

CSR Test and Coverage Generation

- Automatically generates positive and negative test scenarios

- It verifies end-to-end CSR behavior, including HW–SW interaction, ensuring correctness beyond standalone register validation

- Ensures all coverage bins are hit, leaving no scenario unverified

- Provides ~100% code and functional coverage out-of-the-box for CSR, CPU peripheral and Hardware Software Interface

- Supports custom sequences via GUI or PSS for advanced scenarios

- Provides option to use AI**2 to create HW side signal patterns

This guarantees comprehensive validation with minimal manual effort.

CPU Peripheral and Protocol Verification

IDS-Verify includes built-in VIP support for: AMBA AXI (Full & Lite), AHB (Full & Lite), and APB. It automatically generates protocol-aware verification environments, ensuring complete Hardware Software Interface coverage including corner cases.

Hardware Software Interface

IDS-Verify models data flow from user application logic through the hardware interface into the CSR register bank. It automatically generates volatile tests to validate hardware-driven register behavior, ensuring correct data integrity and robust hardware–software interaction, including corner cases.

Ensuring System-Level Correctness with Automated Debug and Flow

IDS-Verify goes beyond register-level verification by detecting integration issues such as missing connections, incorrect mappings, and incomplete logic, while validating CSR behavior across IP, SoC, and application logic to ensure system-level correctness. It provides clear and actionable debug insights by showing what is working and what is failing, and enabling faster root-cause analysis, thereby improving overall debug efficiency.

With the specification as the single source of truth, any change automatically regenerates the testbench, tests, coverage, and assertions, eliminating mismatches and ensuring correct-by-construction verification. Additionally, IDS-Verify enables a seamless push-button verification flow with simulation-ready Makefiles, integration with IDS-Batch CLI, and support for continuous integration/continuous deployment (CI/CD) workflows, allowing users to run a single command and generate coverage reports instantly

Key Benefits

| Automatic CSR Verification Environment | Hardware Software Interface Coverage | Effort and Time Savings | Additional Advantages |

|---|---|---|---|

|

|

|

|

Who Is It For

- ✔IP, SoC, and FPGA design teams

- ✔Verification teams targeting fast coverage closure

- ✔Teams without dedicated UVM expertise

- ✔Small or resource-constrained teams needing automation

- ✔Organizations aiming to reduce verification cost and effort

IDS-Verify enables a specification-to-sign-off verification flow by automating CSR, CPU peripheral interface and hardware–software interface validation.

By generating complete CSR verification environments, automatic tests, and coverage models directly from specifications, it eliminates manual effort, ensures consistency, and accelerates verification closure.

Operating in the critical path of the ASIC design cycle, IDS-Verify empowers teams to achieve reliable, scalable, and efficient CSR verification with near 100% coverage and minimal effort.

What Our Clients Say