PORTABLE STIMULUS STANDARD (PSS) COMPILER

Portable Stimulus Standard (PSS) Compiler

While every aspect of electronic design automation (EDA) tools has been dramatically improved over time, perhaps no domain has evolved more than verification. It started with hand-written tests using 1s and 0s, upgraded to scripted tests, and took a big leap with constrained-random testbenches. Portable stimulus is the next major step in this evolution.

The idea behind portable stimulus is that a single specification of verification intent should be able to drive every aspect of verification and validation. Without such a specification, there is a great deal of manual work. The Universal Verification Methodology (UVM) made it easier to reuse IP/block testbenches and tests across projects, an important capability but not nearly enough.

More than UVM is Required

Even with all the advantages of UVM, verification engineers must work hard to adapt IP-level models for a subsystem or a full chip. Only a few testbench components can be reused directly at higher levels of the design hierarchy. Embedded programmers must write C/C++ code to do many of the same things to the IP, such as configuring and controlling it to perform its intended functionality.

The testbench and embedded code run together in pre-silicon validation, and considerable manual work is needed to tie the components of this simulation together. The activities of the UVM models and the code must be coordinated to perform the desired tests and check the results. This entire process must be repeated every time that the chip specification changes due to ripple effects on verification and validation.

Finally, after the chip is delivered from the foundry, post-silicon validation is performed in the bringup lab. There is no testbench at all at this point, and the embedded code often must be modified from the pre-silicon version in order to develop production drivers and firmware. The net effect is that the project team codes the same functionality several times, with very limited reuse.

Portable Stimulus Comes to the Rescue

Portable stimulus was invented precisely to solve these problems. The concept is straightforward: enable EDA tools to generate UVM testbenches, models, and tests as well as embedded software written in C/C++ and other languages. After a few pioneering portable stimulus tools were successful on large chip projects, there was industry interest in a standard specification format.

The Accellera Systems Initiative, which developed SystemVerilog and many other standards, tackled this new challenge. In June 2018, they released the first version of the Portable Stimulus Standard (PSS). PSS 2.1 was introduced in 2022, and the Portable Stimulus Working Group (PSWG) is very active in continuing to evolve the standard. Agnisys is a member of PSWG and monitors this work closely.

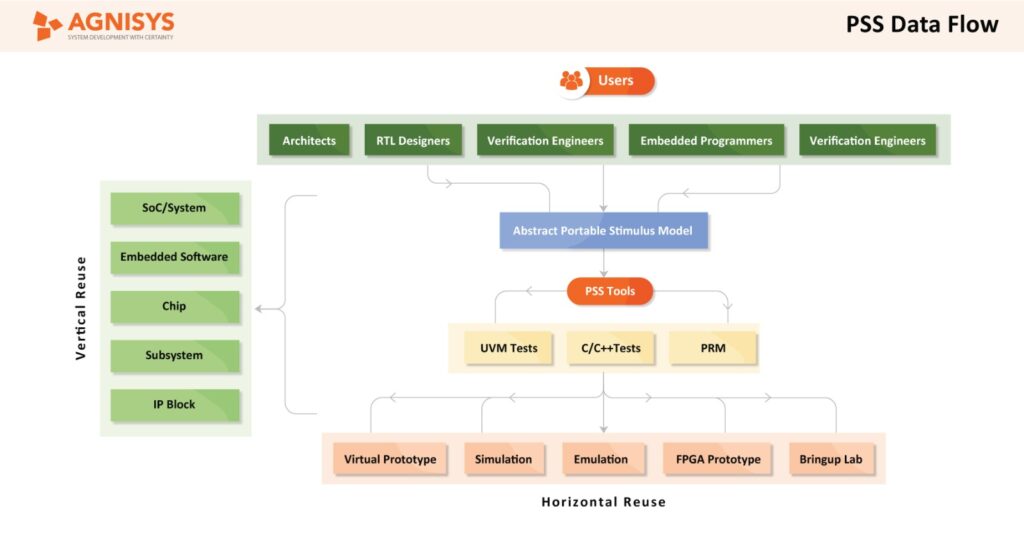

PSS enables abstract, portable specification of verification intent and the automatic generation of tests that work “vertically” from block to system and “horizontally” from simulation to silicon. The figures below shows this portability in a diagram developed by Accellera. EDA tools read a PSS model and generate tests for the selected levels of hierarchy and target platform.

Agnisys Offers Innovative PSS Compiler

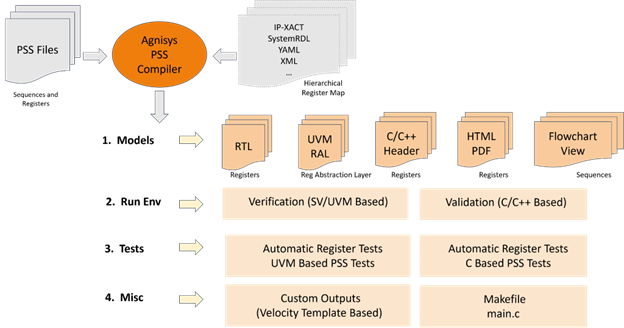

PSS specifies many aspects of verification, but two areas are highly relevant for the solutions provided by Agnisys. Both the architecturally visible registers in an IP or chip design and the sequences that configure and program these registers can be specified with PSS. Verification engineers and embedded programmers no longer have to define registers and sequences manually and independently.

PSS is one of the many input languages and formats accepted by the Agnisys IDesignSpec™ family of specification automation solutions. The Agnisys PSS Compiler provides this support, handling all the constructs required for register and sequence specification. IDS-Validate™ includes both PSS Compiler and an intelligent PSS editor built on the widely adopted Visual Studio (VS) Code platform.

With a PSS model of their registers and sequences, PSS Compiler enables Agnisys users to automatically generate UVM testbenches, register abstraction layer (RAL) models, and tests for verification and pre-silicon validation. For pre-silicon and post-silicon validation, they generate C/C++ tests that run on the embedded processors within the IP or chip design.

The generated tests span horizontally from high-level architectural simulations to real silicon in the bringup lab and vertically from IP blocks to the complete system. Users can run UVM simulations on the register blocks standalone and then run corresponding embedded tests on a multi-chip board in the bringup lab. There’s no recoding required; the same PSS model is used to generate all files.

Agnisys Provides Unique Benefits

Agnisys generates many more output files than would a pure PSS tool. These include the register-transfer-level (RTL) register design ready for logic synthesis, automatic tests appropriate for the register types, and end-user documentation. All standard register formats such as IP-XCAT and SystemRDL can be generated as well.

The IDesignSpec Suite offers users many ways to specify registers and sequences for automatic generation of tests. Users may have a mix of register and sequence specifications in PSS and other formats. IDS-Validate can automatically merge them together in the generated output tests for both SystemVerilog/UVM and C/C++.

IDS-Validate has been generating both testbenches and embedded code from a single specification for years, so Agnisys is one of the industry’s pioneers in portable stimulus. By supporting PSS both as a specification input format and a generated output format, Agnisys leverages all the advantages of this cutting-edge standard and interoperates easily with other PSS-based EDA tools.

Agnisys + PSS = The Answer

Verification and validation consume an ever-high percentage of the schedule and cost for a chip or IP project. PSS provides significant help via an abstract, portable specification of verification intent that can be leveraged in many ways. Agnisys provides robust, proven specification automation solutions that support PSS for registers and sequences. The combination is unparalleled in the industry. Click here to to view visual studio marketplace