IDS-VerifyTM

Test and Testbench Specification Automation

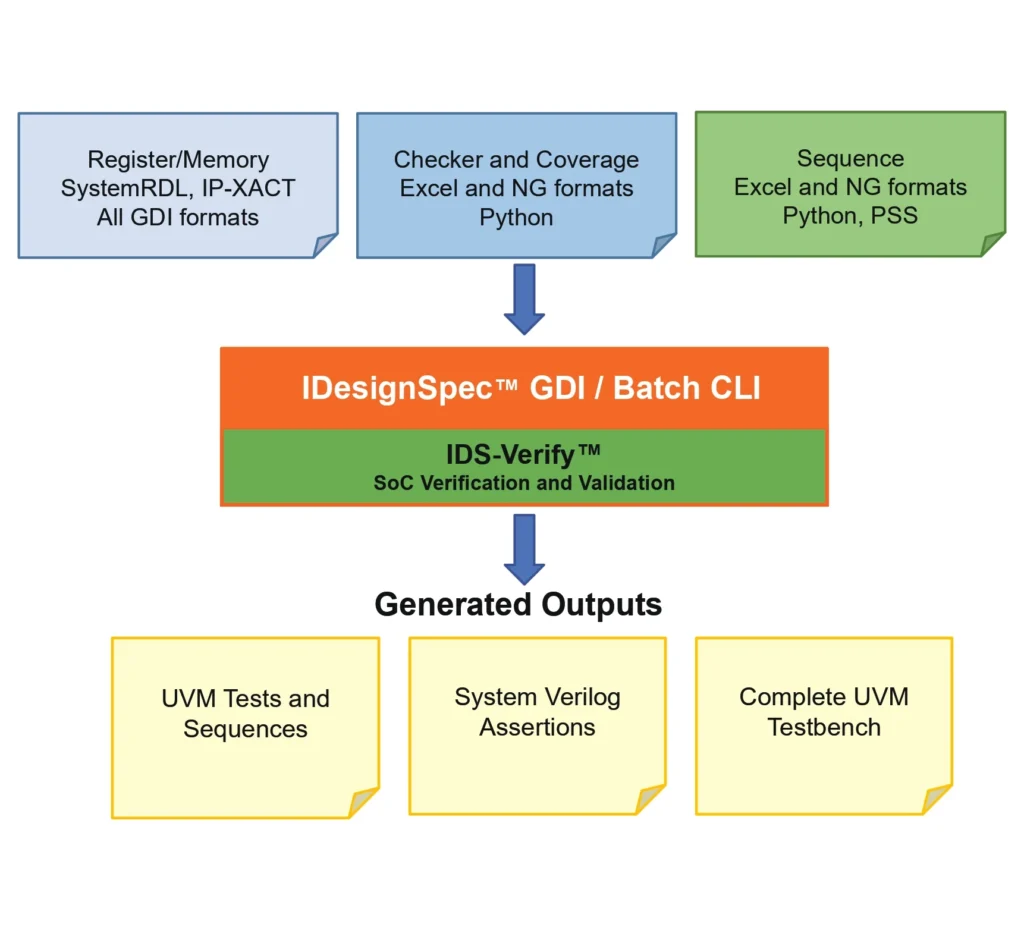

IDS-Verify is a specification-driven verification solution that enables automated CSR (Control and Status Register) and hardware–software interface (HSI) verification for modern IP and SoC designs. It converts register specifications directly into a complete, simulation-ready verification environment, including UVM testbenches, verification sequences, coverage models, and assertions, enabling teams to achieve CSR verification sign-off efficiently and consistently.

Verification teams often spend weeks or even months building testbenches, writing sequences, and iterating to meet strict 100% coverage goals for CSR and HSI verification. This process is highly repetitive and resource-intensive, often involving manual testbench development, custom scripts, and continuous effort to maintain alignment between specification, design, and verification. Integration challenges across IPs, tools, and teams, along with repeated verification effort for every design iteration, further increase engineering effort and delay sign-off, ultimately impacting time-to-market.

Continuous Alignment Between the Specification and Tests and Testbench Code

Fortunately, Agnisys has IDS-Verify, a specification solution for automatic register test, custom register-based sequences, and testbenches in simulation as well as formal verification of registers.

How IDS-Verify Enhances Your Development Process

.

Syntax and semantics checker and debugger

Automatic generation of testbenches for verification

The generated testbench is fully compliant with UVM, including bus agents, monitors, drivers, adaptors, predictors, and sequences, as well as Makefiles for common simulators. The UVM testbench is connected to the UVM register model and RTL design generated by IDesignSpec GDI, providing pushbutton verification.

Automatic generation of sequences

The generated UVM testbench can include sequences, configuration, checkers, coverage, assertions, and inter-component “plumbing” for your design in addition to memories and registers.