Integration is Key for the Adoption of Specification Automation

I frequently delve into the solutions Agnisys offers for the seamless generation of design, SoC verification, testing, software, validation, and documentation files from executable golden specifications, incorporating key industry terms like UVM testbench, IP-XACT, and PSS Compiler. In a recent post, we provided a comprehensive overview of our IDesignSpec™ Suite, underscoring its compelling advantages for your chip and IP teams. Our approach supersedes the traditional practice of manual specification development. Today, I aim to address and demystify the obstacles to adopting this innovative approach and how we’ve meticulously tackled them during our product development.

Unlocking the Benefits of Specification Automation

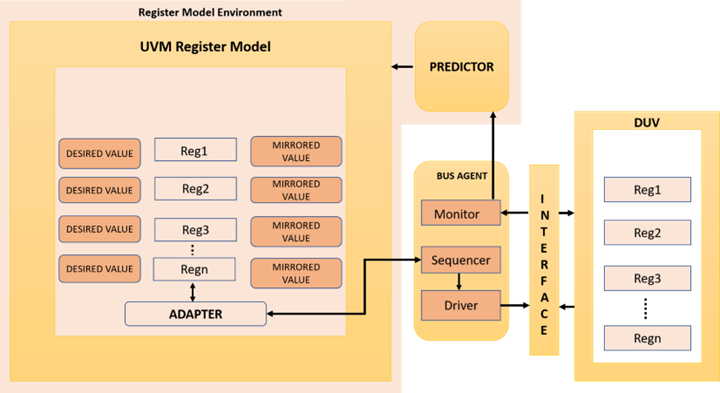

If you haven’t visited our website recently, it’s time to reacquaint yourself with the remarkable advantages our solution offers to your development teams. These advantages can be distilled into three pivotal benefits: heightened efficiency, streamlined development, and elevated design quality. Specification automation lies at the heart of these benefits, greatly enhancing the productivity of your engineers and programmers. Every file we generate from executable specifications translates to less manual work for them. These generated files extend beyond the register-transfer-level (RTL) design; they encompass verification models, UVM IP integration, testbenches, C/C++ code, and user-friendly documentation.

Continuous Value of Automated Generation

The beauty of automated generation lies in its ongoing value throughout a chip or IP project. Whenever your specifications evolve, a chain reaction necessitates updates in design, verification, software, validation, and documentation files. In conventional workflows, manual updates drain precious time and resources. Our automated approach eliminates this painstaking effort, making the process significantly more efficient. Moreover, it safeguards your teams from falling out of sync. You’ll bid farewell to the time spent debugging design discrepancies caused by UVM SoC testbench misalignment or test mismatches with the RTL code. Our solution ensures that every team receives consistent, automated updates at the mere push of a button whenever a specification evolves.

Precision and Quality Assurance

The ultimate and, arguably, the most critical benefit lies in the inherent correctness of your design. The automatic generation of RTL files guarantees their alignment with your specifications. This precision extends to your verification environment and C/C++ code, ensuring seamless UVM IP integration. An accurate verification and validation flow serves as the bedrock of a high-quality design. This holistic process seamlessly integrates, furnishing your teams with a substantial edge over manual development workflows. The success stories of many users underscore the tremendous value of our solution.

Integrating Specification Automation into Your Workflow

You might be inquiring why the adoption of specification automation isn’t universal as of today. The annals of chip development underscore that every substantial innovation has grappled with initial hurdles in adoption. This pattern, evident in past innovations like automated layout, logic synthesis, and constrained-random testbenches, persists. The advent of specification automation is no exception, occasionally provoking concerns regarding its harmonious assimilation into established development ecosystems. Drawing from discussions with prospective users, these concerns crystallize into three primary issues: file formats, integration with existing tools, and ease of use.

The first issue that engineers raise pertains to the compatibility of their file formats. Chip designs manifest in a spectrum of languages such as Verilog, SystemVerilog, VHDL, or SystemC. IP-XACT principles guide the majority of UVM Testbenches, mandating adherence to the Universal Verification Methodology (UVM) standard. Furthermore, the amalgamation of C/C++ code frequently enters the equation, notably in system drivers interacting with the design. In the context of system-on-chip (SoC) development, C/C++ code execution during pre-silicon validation in simulation or emulation, post-silicon validation in the bring-up lab, and operational phases in the field become pivotal. The scope broadens further with documentation encompassing HTML, PDF, Markdown, and DITA formats.

Specifications can be authored and shared through various mediums, from SystemRDL to C/C++, IP-XACT, YAML, JSON, RALF, and CSV files. Some users yearn for support that extends to interactive platforms like Microsoft Word, Microsoft Excel, or OpenOffice Calc. The ears of our development team are attuned to user needs, and our IDesignSpec™ Suite seamlessly caters to this multifaceted landscape. In addition, we equip you with a potent graphical editor that facilitates the creation and modification of specifications. When you embark on the journey of specification automation with our solution, there’s no need to relinquish or alter the formats cherished by your design, verification, programming, validation, and documentation teams.

Preserving the existing file formats isn’t the sole aspiration of users. They seek to retain their established project tools, the same tools they relied on in manual workflows. Importantly, all files generated by our solution harmoniously integrate with standard EDA tools, encompassing simulation, formal verification, design checking, logic synthesis, and more. Our compatibility extends to popular revision control systems, bug-tracking systems, and project management tools. We’ve even meticulously tailored an integration with the widely embraced Git version-control system. Notably, many of our esteemed customers have seamlessly introduced our solution into advanced continuous integration (CI) and continuous deployment (CD) workflows.

Our commitment to ease of use is unwavering. We’ve invested substantial efforts to ensure that our products are not only intuitive but also swiftly adaptable with minimal training. The support we extend for existing formats and workflows means that there’s no necessity to delve into new languages or reshape your project management strategies. Our user-friendly graphical interfaces facilitate instant productivity from day one. Rest assured, the benefits of specification automation will begin accruing immediately upon your adoption of our solution.

Start Today!

I trust that I’ve intrigued you by outlining the key benefits of specification automation and that I’ve allayed any concerns that you may have about how easy it will be to integrate into your existing chip or IP development flow. I invite you to get started today. Please contact us to learn more, request a demonstration, or get a complete diagram of our input and output format support. We look forward to hearing from you very soon.