Role of IP-XACT Standards for Efficient Manufacturing of IPs and SoCs

Chip designers have always reused circuitry, when possible, to shrink the project schedule, save resources, and reduce risk by using a silicon-verified design. Many types of chip design elements are common in diverse applications, and gradually these became packaged into libraries shared across all the teams in a company. The advent of register-transfer-level (RTL) descriptions made reuse much easier since logic synthesis tools could map the same code to many different silicon technologies.

Rise of Reusing IP Chips

In the 1990s, internal reuse was complemented by a robust commercial silicon intellectual property (IP) industry, in which both digital RTL cores and hard macros for analog elements were licensed to many different customers. Chip designers could focus their time and effort on differentiating features rather than common functions where custom chip design yielded no competitive advantage. Today’s large system-on-chip (SoC) designs contain hundreds or thousands of design blocks and could not be developed efficiently without the use of commercial IP.

The History of IP-XACT Standard

The evolution of the IP-XACT standard has closely paralleled the dynamic growth of the semiconductor industry. Originating from the imperative need to define design blocks consistently, facilitating their evaluation for System-on-Chip (SoC) applications, the IP-XACT standard emerged through the pioneering efforts of the SPIRIT Consortium, now an integral part of the esteemed Accellera Systems Initiative. IP-XACT 2022 standards continue to be at the forefront of semiconductor design.

IP-XACT, as an XML-based standard, plays a pivotal role in describing intellectual property (IP) blocks, simplifying their integration into SoCs and smaller chips. Its core objectives are listed below:

- Ensuring compatibility across diverse component descriptions from multiple vendors.

- Promoting the exchange of intricate component libraries among Electronic Design Automation (EDA) tools for SoC design.

- Detailed depiction of configurable components through metadata.

- Facilitating the development of EDA vendor-neutral scripts for component creation, generation, and configuration.

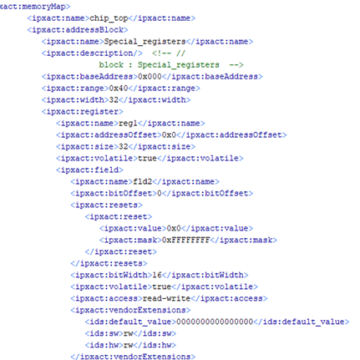

In 2022 IP-XACT iteration, is commonly used by numerous companies, serving as the definitive framework for defining and elaborating on components, system architectures, bus interfaces, and connections. It also abstracts these buses and delves into component specifics, such as address maps, register and field descriptions, and file sets. This standard’s application extends to automating design, verification, documentation, and utilization workflows for electronic systems.

This comprehensive standard includes XML schemas compliant with World Wide Web Consortium (W3C) standards and augmented by semantic consistency rules (SCRs). Additionally, it offers a portable generator interface that seamlessly traverses various tool environments. The synergy of methodology-independent metadata and tool-agnostic mechanisms empowers portability across design data, methodologies, and environment implementations, ensuring a cohesive and efficient semiconductor design landscape.

Agnisys and IP-XACT Standard: The Powerful Duo

IP-XACT standard has become especially popular as a way to describe the architecturally visible registers that form the hardware side of the HSI in an IP block or a complete SoC. Manually writing the RTL for the register design from an IP-XACT definition is more precise than from a specification written in natural language, but it is still a tedious and error-prone task. With a specification automation tool, the IP-XACT standard file serves as a single, golden executable specification from which the design is generated in a correct-by-construction approach.

The Agnisys IDesignSpec Suite leverages the IP-XACT standard to capture the register information and generate the verified implementation in synthesizable RTL form (Verilog, SystemVerilog, VHDL, or SystemC). It also generates a Universal Verification Methodology (UVM register model, testbench, test sequences, C/C++ header files, test sequences, and high-quality documentation suitable for end users. Using the IDesignSpec Suite and a single source file eliminates RTL coding errors and reduces the risk of ambiguous functionality or inconsistencies between the design and testbench.

At Agnisys, we work with a wide variety of users and we frequently come across register types that are beyond the scope of standard IP-XACT. Fortunately, our users can still describe these special features in IP-XACT using the vendor extension (VE) mechanism. Register types such as alias, Interrupt, counter, paged, trigger buffer, custom connections, and UVM properties have been implemented using VE.

Of course, users can specify registers using other formats, including SystemRDL, spreadsheets, and our intuitive register editor. In these cases, we generate IP-XACT output files to make it easy to interact with other tools supporting the standard.

Why Choose Agnisys?

Our solutions improve the performance of all teams involved in an IP or SoC project. The key benefits of using the IDesignSpec Suite with IP-XACT standard include:

- Reading in existing IP-XACT files to leverage existing register descriptions

- Writing our IP-XACT files for registers specified using other input formats

- Automatically verifying all addressable registers in the design to ensure that the generated register code is correct

- Creating synthesizable register RTL code for design teams and keeping it synchronized and requirements change

- Enabling faster and more accurate device driver, firmware, and application software development

- Eliminating errors in communication of interfaces between functional teams

- Automatically creating product documentation for users and technical publications

- Improving the productivity of engineers and the quality of results

- Supporting architecture, design, verification, SoC validation, diagnostics, firmware, application software, and documentation teams