Specification Automation to Accelerate Embedded SoC Development

In today’s semiconductor industry, the most interesting and challenging chips are embedded SoCs. I think it’s worth mentioning that “embedded” and “SoC” sometimes have different connotations. An embedded system is generally considered a system that contains one or more processors running code that is usually considered lower level than operating systems and full user-level applications. Of course, that is changing as embedded processors become ever more powerful and applications ever more demanding.

So, an embedded system contains both hardware and software, and an embedded chip has it all within a single device. But isn’t that really the same thing as a system on chip (SoC)? Most people would say that any SoC must contain one or more processors (therefore embedded) running code (also embedded) so we’re right back where we started. I mention this to make an important point: the once specialized embedded domain has been subsumed into the general world of chip design and accompanying software development.

Developing Embedded SoCs

I also raise this topic to acknowledge that the solutions we provide are aimed squarely at embedded SoCs. These chips present enormous challenges at every stage of development, regardless of the underlying technology. Today’s FPGAs are almost certainly full SoCs. Although they don’t require refabrications to fix bugs, finding and fixing issues in the bring-up lab takes tremendous effort, delaying time to market (TTM) as surely as a chip turn. Thus, everyone faces similar challenges and is looking for similar solutions to accelerate embedded development while maintaining quality.

Any solution must cover both hardware and software, spanning design, verification, software, validation, and documentation. Specification automation, our main area of expertise, is the only robust, proven solution that meets all the requirements. The flow starts with executable specifications for many parts of the SoC, either leveraging established formats such as IP-XACT and SystemRDL or using AI-based tools to extract executable content from natural language datasheets. This creates a single golden specification source that can benefit every team on the SoC project.

With executable specifications, significant amounts of SoC hardware and software can be generated automatically. This saves manual engineering effort and shortens the schedule. It also eliminates errors created by misinterpretation of specifications or differing interpretations by different teams. No longer will programmers write code that doesn’t properly access the control and status registers (CSRs) in the hardware design. Further divergence errors are prevented by simply repeating the generation process whenever a specification changes, which happens many times in a typical project.

Generation from the Specifications

So what sort of hardware and software files can be generated automatically from golden executable specifications? For a start, complete register-transfer-level (RTL) designs for CSRs, their bus interfaces, clock-domain-crossing (CDC) logic, and safety mechanisms that detect and respond to chip failures. A complete specification automation solution must also be able to generate IP blocks for standard functions, along with the RTL code to interconnect both generated and designer-written blocks into a fully assembled top-level chip design.

Any hardware design must be verified, and the solution must also be able to generate Universal Verification Methodology (UVM) testbenches and tests to program and test the CSRs. Generating assertions to verify the IP interconnections in simulation and/or formal verification is also valuable. Hardware and software can be co-verified in a pre-silicon validation environment that supports a UVM testbench along with executing embedded code. The specification automation solution must also be able to generate this environment.

Portions of the C/C++ embedded code that access the CSRs can be generated automatically as well. This code can be used to test the registers from the software side and can run in both the pre-silicon validation environment and as part of post-silicon validation in the bring-up lab. The CSR code can also serve as a starting point for the production of embedded programs such as drivers and firmware. Finally, it must be possible to generate high-quality CSR documentation suitable for incorporation into the end-user manuals developed by technical writers.

The Agnisys Solution in Action

Everything I’ve just described for a specification automation solution is available from Agnisys today. Our IDesignSpec™ Suite automates the design, verification, programming, validation, and documentation of CSRs, standard IP blocks, and chip assembly. This saves precious engineering time and resources for every team at every phase of the embedded SoC project. Teams always remain in sync, using a common, golden specification process. We provide training, methodology, and applications engineering support to ensure that every user is successful.

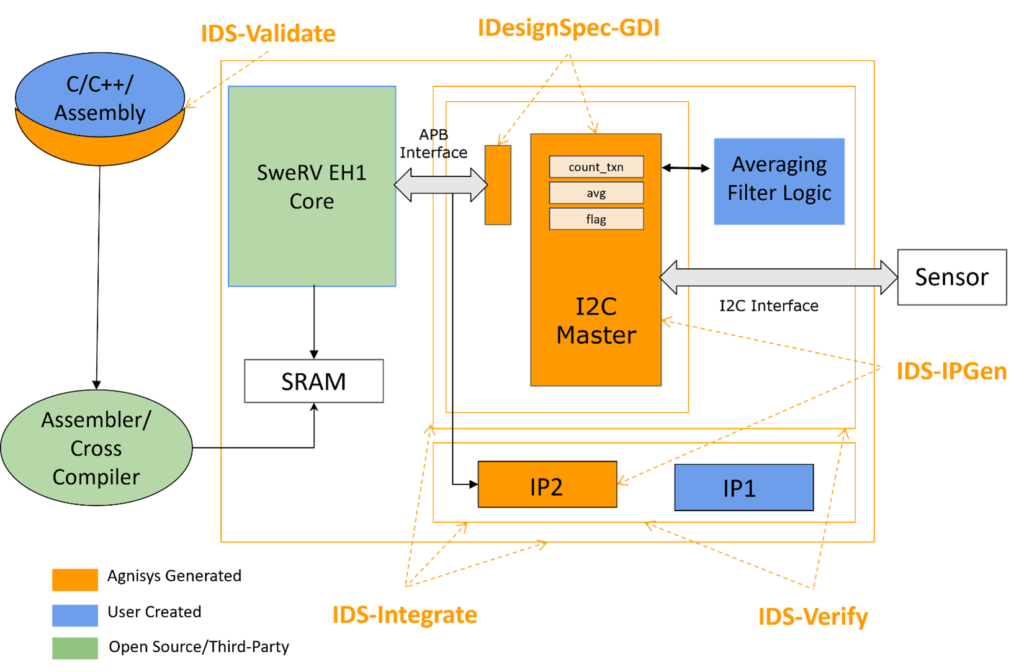

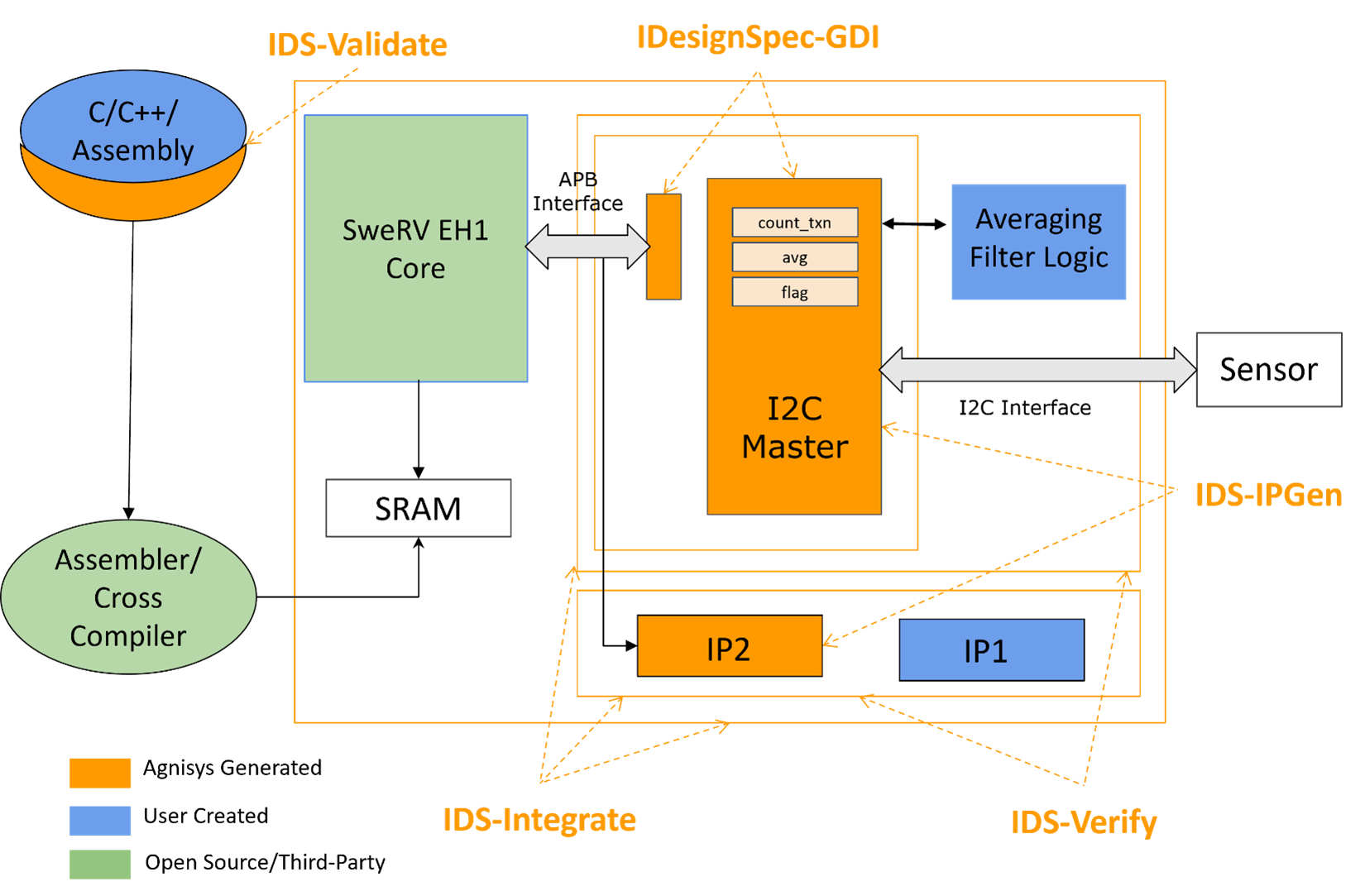

To demonstrate the value of our flow, we created our own small SoC design. It averages sensor data received over an I2C interface. Sensor values are read in and converted into an averaged value by user application logic, all under control of software running on a CPU. The diagram below shows the design and where our tools were used in the flow. The CPU is the open-source SweRV Core EH1, a 32-bit, 2-way superscalar, 9-stage pipeline implementation of the RISC-V architecture. Other than this core and the averaging RTL and software, the entire project was automated using our unified flow:

- Our IDesignSpec-GDI family generated the RTL for the CSRs and the APB interface to connect to the CPU

- Our IDS-Integrate™ smart SoC assembly tool connected all the blocks together and created the top-level RTL design

- Our IDS-Verify™ generated the complete UVM simulation environment, including register model, agents, coverage, and test sequences

- Our IDS-Validate™ generated a synchronized C-UVM verification environment and the embedded C code to verify the CSRs

The Agnisys solution has been used successfully on more projects that I can count, and we’re signing up new users all the time. If you’re not already part of our family, let us know if you’d like to see a demo or try our solution. I’m certain that you will be a user for your next embedded SoC project.