Power of SystemRDL to IP-XACT Conversion: Streamlining IP Integration

In the ever-evolving landscape of semiconductor and electronic design, the pursuit of efficiency, consistency, and reusability remains paramount. Designers frequently grapple with the intricate task of seamlessly integrating complex Intellectual Property (IP) blocks into their designs while simultaneously aiming to reduce development time and preserve the integrity of their designs. This is precisely where the transformative potential of converting SystemRDL (Register Description Language) to IP-XACT (Intellectual Property eXchange – Abstract Core Technology) comes into play.

This blog will delve deep into the profound significance of the SystemRDL to IP-XACT conversion process, shedding light on how it serves as a pivotal linchpin for streamlining IP integration. By exploring this transformative process, we aim to illustrate how it modernizes and elevates the design process in the context of the ever-advancing electronics landscape. In this exploration, we will also touch upon the key distinctions between SystemRDL and IP-XACT, and how the evolution to SystemRDL 2.0 brings further advancements to this critical domain.

Understanding SystemRDL and IP-XACT

SystemRDL

SystemRDL, a widely adopted language in the realm of electronic design, serves as a powerful instrument for describing and managing registers within digital systems, especially concerning hardware registers. This language equips designers with the means to effectively define the architecture, functionality, and attributes of records within an Intellectual Property (IP) block. In essence, SystemRDL enables the comprehensive specification of register bit-fields, access policies, constraints, and various other critical elements. It proves to be an indispensable tool in the arsenal of IP developers, facilitating the intricate process of crafting IP components.

SystemRDL Compiler and Parser

To harness the full potential of SystemRDL, designers often rely on specialized tools known as SystemRDL compilers and parsers. These tools are instrumental in the interpretation and manipulation of SystemRDL code, allowing for seamless integration of the defined registers and their associated properties into the larger design context. A SystemRDL compiler is responsible for translating the descriptive SystemRDL code into a format that can be utilized in the design process. Conversely, a SystemRDL parser plays a pivotal role in extracting essential information from SystemRDL descriptions, enabling further analysis and utilization within the design flow.

IP-XACT Standard

On the other hand, IP-XACT, as defined by the IEEE 1685 standard, introduces a standardized XML schema that plays a central role in describing and packaging Intellectual Property (IP) at varying levels of abstraction. This standard encompasses a comprehensive set of metadata, configuration details, and hierarchical structures, making it a robust and versatile choice for expressing IP components for a multitude of purposes. Its overarching objective is to provide a consistent framework for IP representation that extends to integration and interoperability between different design environments.

IP-XACT Quality

Ensuring the quality of IP-XACT representations is of paramount importance in the electronic design landscape. The quality of IP-XACT documents directly impacts the reliability and effectiveness of IP integration efforts. It involves adhering to best practices and guidelines defined by the IP-XACT standard, which encompass aspects like accurate metadata, correct configurations, and precise hierarchical structuring. Maintaining high IP-XACT quality is not only an industry best practice but also a critical element in the pursuit of efficient and trouble-free IP integration within diverse design projects.

The Power of Conversion: SystemRDL to IP-XACT

Converting SystemRDL to IP-XACT involves the transformation of register descriptions and associated metadata from SystemRDL into the standardized IP-XACT format. This conversion holds immense power and brings several advantages to the IP integration process, seamlessly bridging the realms of design and interoperability.

Enhanced Reusability: One of the foremost benefits of this conversion lies in the enhanced reusability it affords. By translating SystemRDL descriptions into IP-XACT, IP blocks can be effectively reused across different designs, projects, or organizations without the need for manual adjustments or extensive rework.

Tool Interoperability: IP-XACT enjoys strong industry support and is compatible with a wide array of design tools. Converting SystemRDL to IP-XACT fosters tool interoperability, enabling a smooth collaboration and integration experience across the design flow. It ensures that designs created using SystemRDL can seamlessly interact with other tools and environments.

Improved Documentation: IP-XACT promotes comprehensive IP documentation, encompassing detailed register descriptions and their associated properties. Converting SystemRDL to IP-XACT facilitates the generation of thorough and structured documentation, enriching the understanding of the IP and its integration requirements. It enhances transparency and simplifies the communication of IP-related information.

Future-Proofing IP: As design environments and tools continue to evolve, having IP descriptions in a standard format like IP-XACT is strategically advantageous. The conversion future-proofs the IP, making it compatible with upcoming tools and methodologies, ensuring the longevity and reusability of the IP assets.

Streamlined Integration Process: IP-XACT, with its standardized structure, streamlines the integration of IP blocks. The conversion ensures that the metadata and register descriptions from SystemRDL seamlessly integrate into the overall design, expediting the integration process and enhancing efficiency.

SoC Integration

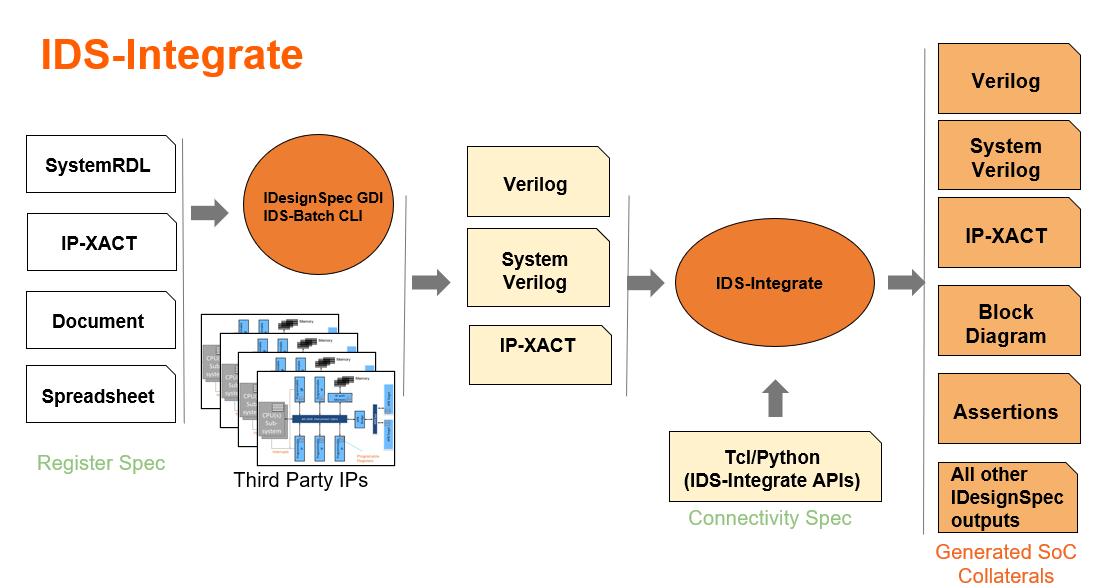

IP-XACT plays a pivotal role in System-on-Chip (SoC) integration. It encompasses bus and abstraction definitions, which specify interface types for hardware communication protocols. Moreover, IP-XACT defines an API known as Tight Generator Interface (TGI) for IP-XACT XML document access and manipulation. This capability serves as a bridge between design tools and third-party TGI generators, facilitating SoC-level assembly and interconnection. It provides a flexible and customizable environment to meet the design requirements for complete chips, supporting the integration of diverse IP blocks and components seamlessly.

In summary, the conversion from SystemRDL to IP-XACT empowers the electronic design industry with enhanced reusability, tool interoperability, improved documentation, future-proofed IP assets, and a streamlined integration process, while also playing a crucial role in System-on-Chip integration. This dynamic transition ensures that design processes remain agile, efficient, and adaptable in a rapidly evolving landscape.

Final Thought

SystemRDL to IP-XACT conversion represents a robust and transformative process within the realm of semiconductor and electronic design. This conversion holds the power to significantly streamline IP integration, offering design teams a multitude of advantages, and revolutionizing the way complex IP blocks are seamlessly incorporated into designs.

By translating SystemRDL descriptions into the standardized IP-XACT format, design professionals can unlock a range of benefits, which include standardized representation, enhanced reusability, improved tool interoperability, a streamlined integration process, comprehensive documentation, and a future-proofed IP. This transformative shift isn’t merely a technical translation; it signifies a move toward standardization, heightened efficiency, and a future-ready approach that can drive the success and efficiency of modern design projects.

For an effective implementation of this conversion process, designers must meticulously select the appropriate SystemRDL to IP-XACT tools, validate the converted IP-XACT, seamlessly integrate it into their design environment, and uphold the importance of proper documentation. With these steps in place, designers can optimize their design workflows, save valuable time, and achieve the seamless integration of intricate IP blocks. This process is instrumental in advancing the semiconductor and electronic design landscape, offering a more streamlined, efficient, and standardized approach to IP integration.