Formal Verification

In our recent Formal Verification webinar explored the crucial role of rigorous verification in ensuring hardware design reliability amidst increasing complexity. We showcased iSpec.ai, leveraging advanced LLMs and innovative techniques like Prompt Engineering and Fine-Tuning to streamline SystemVerilog Assertion generation from plain English requirements. By bridging machine translation with formal verification, iSpec.ai offers a transformative solution to address time-to-market challenges and mitigate risks associated with traditional verification methods.

eBook: How Agnisys Eliminates Redundancies in Semiconductor Design, Verification, and Validation

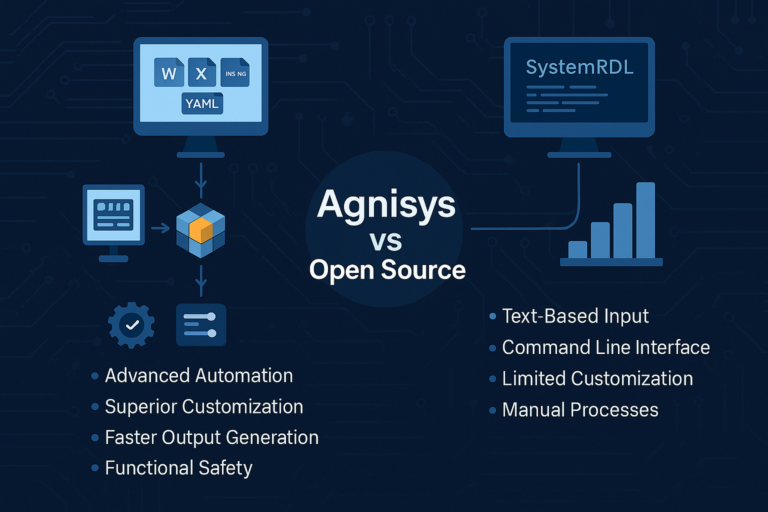

Overcoming the weaknesses of traditional natural language specifications requires writing the specifications in a precise format rather than natural language, and making this format executable so that tools can generate as many files as possible for the design, verification, programming, validation, and documentation teams. Such a solution is available today.

Recent Blog Articles

The Complete One-Stop Solution for Modern SoC Design Challenges In the fast-paced world of semiconductor design, enterprises need robust, flexible...

Agnisys showcases next-generation EDA solutions at DAC 2025, including IDesignSpec Suite v9, IDS-FPGA Launch, AI² and IDS-Integrate Enhancements. BOSTON, MA...

iCatch Technology selects Agnisys’ IDS-Integrate to streamline SoC assembly, ensure design integrity, and accelerate AI chip development. BOSTON, MA, UNITED...