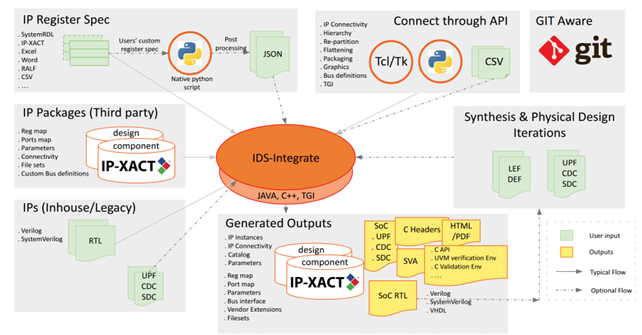

In this webinar, Agnisys showcased IDS-FPGA, a powerful solution designed to automate and accelerate the FPGA development process. Using an Ethernet Generator and Monitor as an example, the session walked through the complete flow—from capturing the design specification and generating synthesizable RTL to automating integration with required ports and interconnects. IDS-FPGA also demonstrated its capability to generate UVM and C-based tests and assertions, ensuring efficient and thorough verification. The webinar highlighted how IDS-FPGA simplifies complex design tasks, reduces manual errors, and enables fast, reliable hardware/software co-design and co-verification.

eBook: How Agnisys Eliminates Redundancies in Semiconductor Design, Verification, and Validation

Overcoming the weaknesses of traditional natural language specifications requires writing the specifications in a precise format rather than natural language, and making this format executable so that tools can generate as many files as possible for the design, verification, programming, validation, and documentation teams. Such a solution is available today.

Recent Blog Articles

In today’s semiconductor industry, the most interesting and challenging chips are embedded SoCs. I think it’s worth mentioning that...

In my most recent blog post, I reminisced about childhood toys that let you construct complex structures from simple...

As kids, many engineers enjoyed toys that involved assembling complex designs from simple elements. Whether it was wooden blocks...