SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

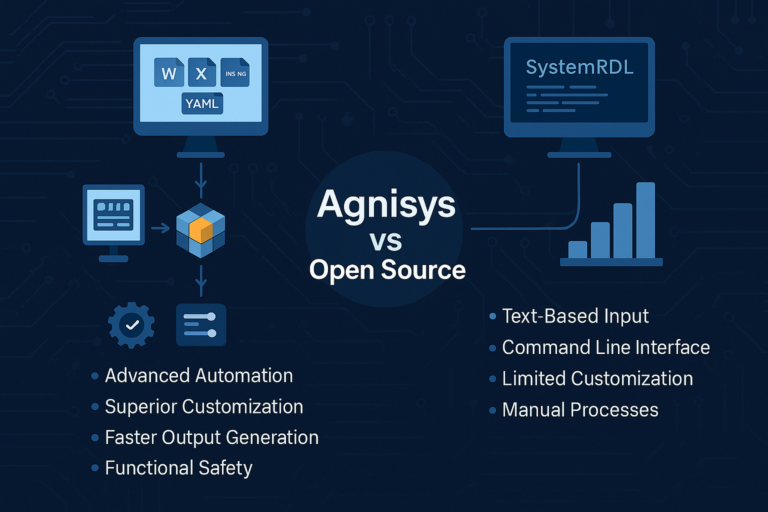

The Complete One-Stop Solution for Modern SoC Design Challenges In the fast-paced world of semiconductor design, enterprises need robust, flexible...

Introduction IDesignSpec (IDS) suite of products can seamlessly integrate into your Vivado projects allowing for faster turnaround times. IDS can...

Join Agnisys for a technical deep dive into IDS-FPGA, a comprehensive solution that automates the end-to-end FPGA development process...

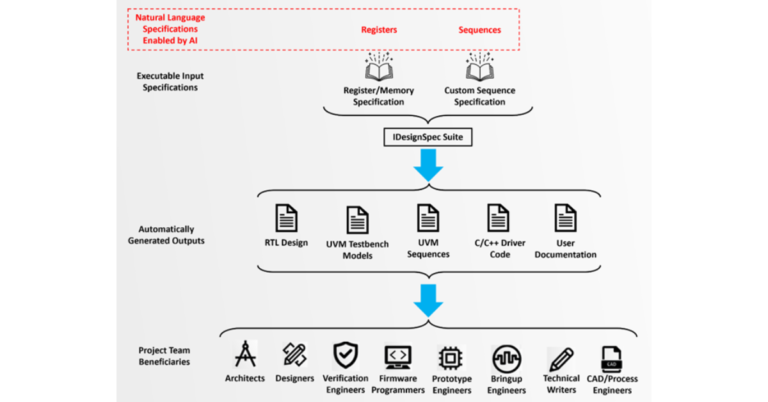

Hardware verification has always been the quiet bottleneck in chip development. For those working in the industry, it’s a...

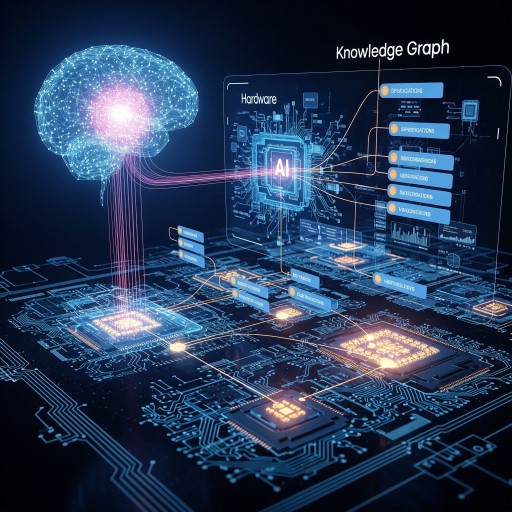

A recent blog post looked at the impact artificial intelligence (AI) is having on chip development, focusing on register-transfer-level...

Taking IP Integration Efficiency to the Next Level Designing modern System-on-Chip (SoC) architectures continues to grow in complexity, particularly...

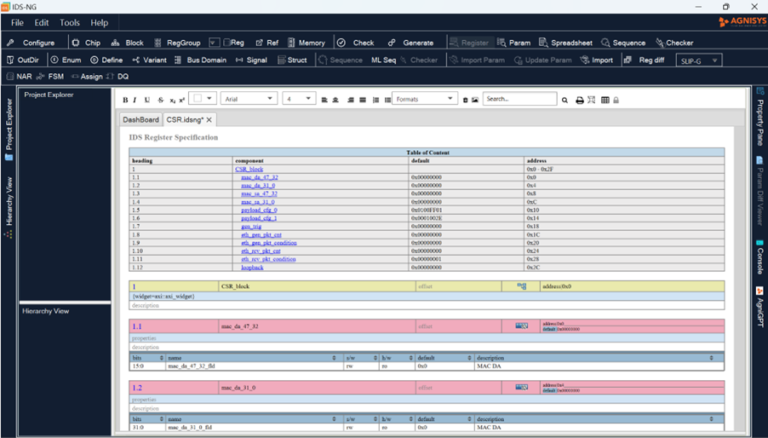

If you search for the definition of CSR, you will likely find “corporate social responsibility” at the top of...

The Challenge of IP Integration in SoC Design In modern System-on-Chip (SoC) design, integrating thousands of Intellectual Property (IP) blocks...

Ever wondered how SoC design teams keep all their files in sync and avoid costly errors? Synchronization of files...