SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

American statesman Benjamin Franklin is famously quoted as saying “in this world, nothing is certain except death and taxes.”...

If I’ve been blogging a lot about artificial intelligence (AI) recently, there are several good reasons for this. Of course...

Over the years, there have been some seismic shifts in the semiconductor industry. Because of the huge quantity used...

Every IP and chip design is created for one reason: to build a successful electronic product. This is true regardless...

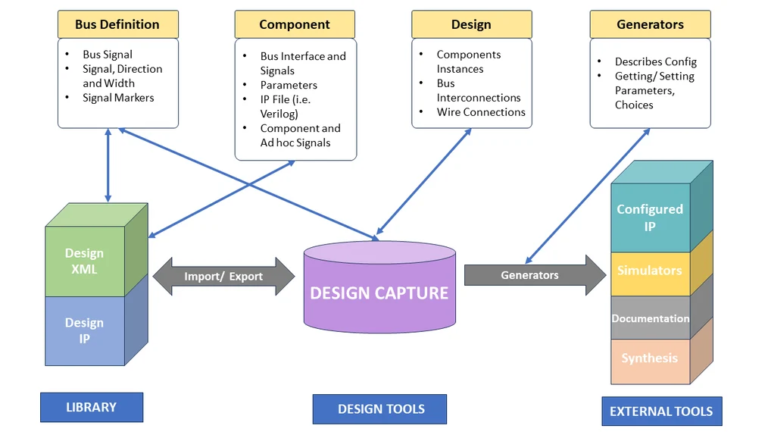

Developing a System-on-Chip (SoC) is a complex process involving multiple steps, iterations, and collaboration across diverse teams. From managing...

System-on-Chip (SoC) development has become a cornerstone of modern electronic design, driving innovation across industries like automotive, consumer electronics, and...

Abstract ISO 26262, derived from the IEC 61508 standard, is critical in ensuring the functional safety of automotive electronic and...

Efficient management of registers and memory maps is critical for the success of modern System-on-Chip (SoC) designs. As SoCs...

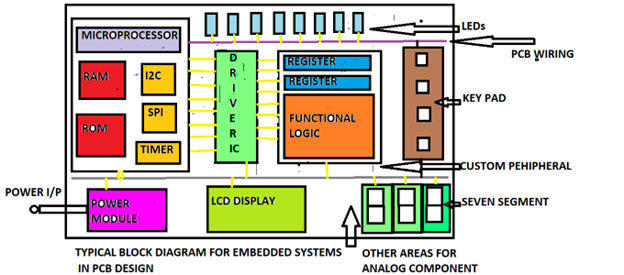

Introduction Usually, Any Digital Peripheral Custom IP is divided into two sections. One is designed logic circuits based on their...