SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

IDesignSpecTM (IDS) is a product suite that improves the productivity of FPGA/ASIC, IP/SoC, and system development teams. These products encompass...

The Agnisys PSS (Portable Stimulus Standard) Extension in Visual Studio Code (VS Code) is an essential tool for hardware verification...

The Agnisys SystemRDL Extension in Visual Studio Code (VS Code) is a powerful tool for hardware designers working with SystemRDL—the...

The Agnisys IDesignSpec™ Suite provides comprehensive clock domain crossing (CDC) circuitry support for both hardware and software. Key synchronization...

Agnisys IDesignSpec™ optimizes low power design through advanced clock gating. By disabling the clock for inactive registers, IDS reduces dynamic...

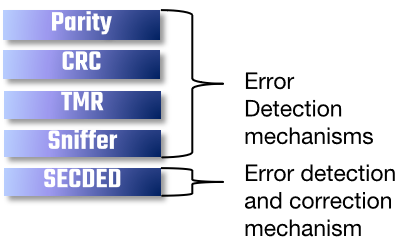

IDesignSpec™ enhances system reliability in safety-critical applications with features like SECDED, which corrects single-bit errors and detects two-bit errors, preventing...

Agnisys IDesignSpec™ facilitates seamless integration of various bus interfaces through automated generation of decoders and bridges, streamlining the design...

IDesignSpec™ provides robust support for complex structures and register types, enabling engineers to define intricate designs with remarkable flexibility...

Agnisys IDesignSpec™ streamlines the design process by interactively generating comprehensive output files tailored for design, verification, software, and documentation teams. From...