SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

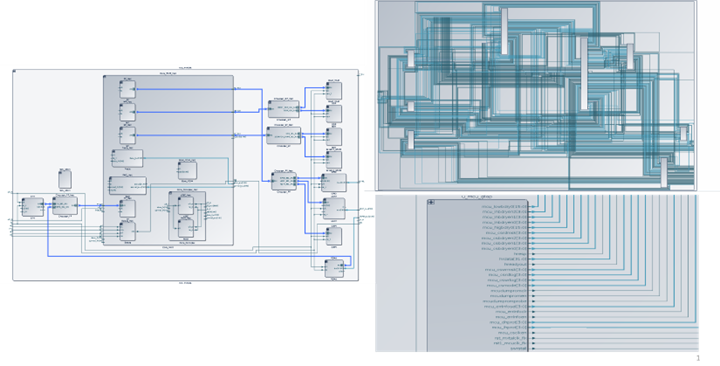

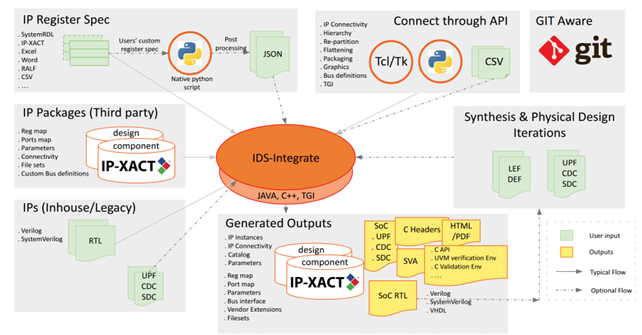

Verification of modern IP and SoC designs presents several challenges. Specifications are often interpreted differently across teams, such as design...

If you’ve worked with Zephyr RTOS, you already know that devicetree files are a core part of how hardware...

In today’s semiconductor industry, the most interesting and challenging chips are embedded SoCs. I think it’s worth mentioning that...

In my most recent blog post, I reminisced about childhood toys that let you construct complex structures from simple...

As kids, many engineers enjoyed toys that involved assembling complex designs from simple elements. Whether it was wooden blocks...

As semiconductor designs grow exponentially in complexity, verification has become the single largest consumer of engineering time and resources...

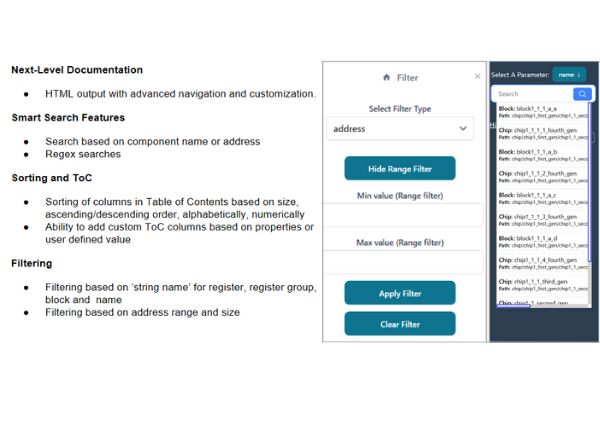

IDS generates rich, interactive HTML documentation hosted within the Collaboration Framework (IDS-CF), enabling fast navigation, smart search, sorting, filtering, and...

IDS generates DFT-aware RTL by introducing configurable control and observe points across critical logic such as read data, address decode...

As you may have seen, we publish quite a few blog posts here on the Agnisys site. We cover...