Semiconductor Register Specification: Shadow of a Shadow

So we have been working in the register specification space for a long time. We came out with the IDesignSpec tool around 2010. Five years of continual refinement, shaped by customer feedback, has resulted in a mature technology capable of addressing any customer’s flow and register requirements. Five years of constant refinement and evolution based on customer feedback has created a very mature technology that can pretty much deal with any flow that the customer needs and any type of register that he needs. Well, so you would think. However, to our amazement, we still, constantly get new requests from new customers who want to add more features to suit their needs. We of course take these new flows new register types and new behaviors with gratitude and incorporate them in the tool to make the tool more versatile.

Great discussions about Semiconductor Register Specification at DVCon

At our booth at DVCon and visits to several new customers in the Bay area we find that many companies are still struggling with Register data and how to come up with a coherent methodology that satisfies all aspects of register data usage. Satisfying diverse teams with varied goals in large organizations poses a unique challenge compared to satisfying a single group of people. And if you come up short, then you will have to revisit this issue in a few years once again.

Some of the requests we received were …

- How to refer to an IP-XACT or SystemRDL file from a CSV file at the top level

- Support for plugins for Excel on MacOS

- Google Docs and LibreOffice, just to name a few

There is also confusion

While some believe the UVM register has resolved all register-related issues, this is a misconception. UVM serves as a solid starting point, but the journey is ongoing. For those unsure of where to begin, I recommend utilizing the Automatic Register Verification (ARV) module to initiate your UVM journey. With ARV, describing registers in SystemRDL, CSV, Word, or Excel goes beyond generating UVM or RTL models—it creates the entire UVM testbench environment, sequences (both positive and negative), agents, makefile, and even a verification plan, ensuring registers behave as expected. On average, UVM standard sequences achieve approximately 55% overall coverage for a mix of register types, whereas ARV surpasses 90%. This seamless process is accomplished with just a click, marking a significant advancement in automation.

The other issue we encountered at DVCon and talking to various companies in the area, was the lack of consistent definition of the special registers. These special registers are what makes this field interesting and how to deal with them in RTL and UVM is always a challenge and cause for debate. One engineer came to me and asked about the Shadow register only later did we discover that he was talking about indirect registers. Another engineer we visited talked about Aliased registers when really what he meant was two different views of the Software. And one area that has more confusion than any other is Interrupts.

I’ll be writing about each of these special register types in my future posts

While any student can create registers in Python, industrial-strength tools like IDesigSpec are essential for handling complex registers effectively.

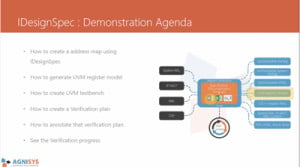

If you bring IDesignSpec into your semiconductor design flow, you will be creating consistent specifications without a shadow of a doubt. If you are not planning to visit DVCon, then please watch our online demonstration video of our semiconductor register specification and verification solution.