Where Tool Ideas Come From – A Case for a Portable Sequence Generator

By Louie De Luna, Agnisys Director of Sales and Marketing

Tools are made to automate a process, perform calculations, minimize errors and improve efficiencies, but at their core, tools are made to solve a given problem. Problems are found as a natural effect of progress. They come from the industry – in some cases from experts, innovators and tool vendors, and often times they come directly from the users or customers. As an EDA tool vendor, we serve highly-intelligent users who know their design and verification problems well as these have become roadblocks in their day to day work. But honestly these problems will not reach the tool vendor if there’s no mutual trust to begin with. I’m not referring to the routine support tickets that are filed, but to the technical problems that openly come up during face-to-face discussions. That’s our case with our portable sequence generator.

A few longtime users of our register generator tool shared with us their need to centralize the creation of sequences. The basic idea is to reuse the successful concept that we have in centralizing the creation of registers from a single spec – this concept has unified the IP, software, firmware, device driver and system integrator teams to work from a single source. Any changes to the register spec would typically only involve re-generation of the RTL, UVM regmodel, UVM testbench, C/C++ headers and documentation from the spec itself using built-in code generators. You don’t have to worry about which design and verification elements are impacted due to the register change, and you don’t have to manually modify a long list of register files to implement the change. Many of our users have found this concept and methodology valuable, so they have asked us to do the same thing for sequences.

Sequences have become a powerful mechanism for stimulus generation used by multiple SoC teams. Although there are many advanced UVM features (UVM sequence library class, sequence arbitration, virtual sequences, to name a few) to increase the reusability and ease of creation of sequences, most SoC teams still lack a centralized and unified flow for creating sequences. Often each team has to manually write sequences in their respective formats simply to repeat the same functionality, which certainly drains a lot of time.

Sequences in UVM are used by hardware engineers for testing custom IPs, sequences in SystemVerilog are used by software developers for testing embedded software running on FPGA prototyping boards, sequences in C code are used by firmware and device driver developers, sequences in Matlab are used for validation purposes, and sequences in ASCII or CSV format are used during post-silicon validation in platforms such as automatic test equipment (ATE). The problem is how to centralize these sequences so that the IP/SoC designer or architect defines the sequence once and generates the same functionality in various formats/language domains that can be used on different platforms.

Enter ISequenceSpec, a portable sequence generator tool that enables users to describe the configuration, programming and test sequences of a device in a single spec and automatically generates sequences that are portable onto platforms such as for simulation, prototyping, emulation, post-silicon validation and ATE.

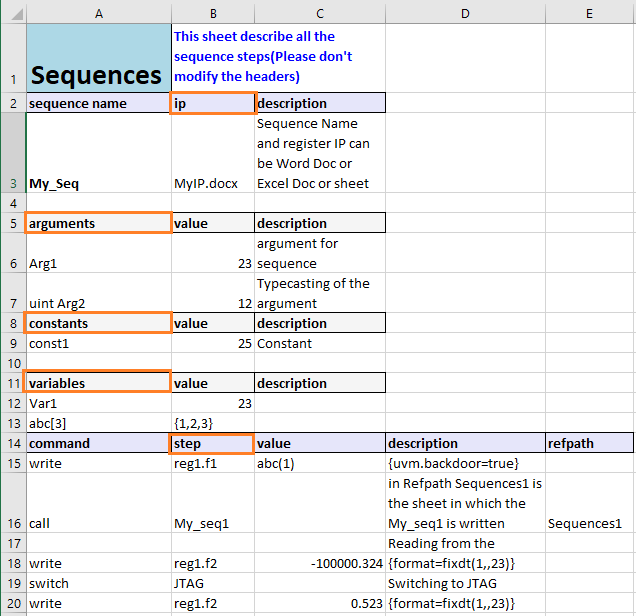

Sequences can be described in a spreadsheet such as Microsoft Excel™ or as plain text. As shown in Figure 1, sequences can be defined using five regions.

- IP – defines the document or sheet in the same workbook containing the register specification and general description of the sequence

- Arguments – refers to the variables or expressions passed from the caller of a macro sequence (or function) into another macro sequence; the macro sequence accepts the argument and returns a sequence back to the calling sequence

- Constants – users can specify various types of number format (binary, decimal, hexadecimal, etc.) as the value of constants

- Variables – can be declared with value or without value, the tool substitutes the body of the variable at each point where the variable is called at run time

- Sequence Steps – users can specify the steps that are needed to be performed sequentially

Sequences can be specified using a rich language and command feature set that includes loops, branch, wait, calls, switch and macros. You can use ternary operators [?, :] to form the sequence step’s values. The ternary function is generated and the output of it is stored in the internal variable assigned to the particular field. Several properties can also be defined for customizing the generated outputs. These properties can be created by using explicit property name-value pair or using the curly bracket syntax in the description. A few useful properties you can define include:

- format – specifies the fixed-data type format of a field

- uvm_door – used for UVM sequences when user wants to write from frontdoor (uvm_door=front) or backdoor (uvm_door=back) to the register model

- uvm.regmodel – specifies the upper hierarchy into the generated regmodel

- num_sites – specifies the number of sites(ICs) used in the LAB in parallel

- site – defines the variable as site-based.

- extern – specifies the variable as global variable

- base_address – specifies the base address of the memory in C

- board_type – defines the board in which the user wants to run the sequences for which signals are used

- signal_map – defines which signal is connected to specific pins of the defined board

A number of semantic problems can occur during the development of a sequence so the tool is equipped with a smart syntax and semantic checker for validating the format and syntax within the specification. The entire sequence specification can be validated and a report containing a complete list of all problems opens in a window for viewing with cross-navigation to the row containing the problem. The checks carried out by the validation process include:

- Register Validation – guides you to the row containing the register problem

- Syntax Validation – Sequence step validation is performed, which checks existence of variables, arguments, in-line functions. etc.

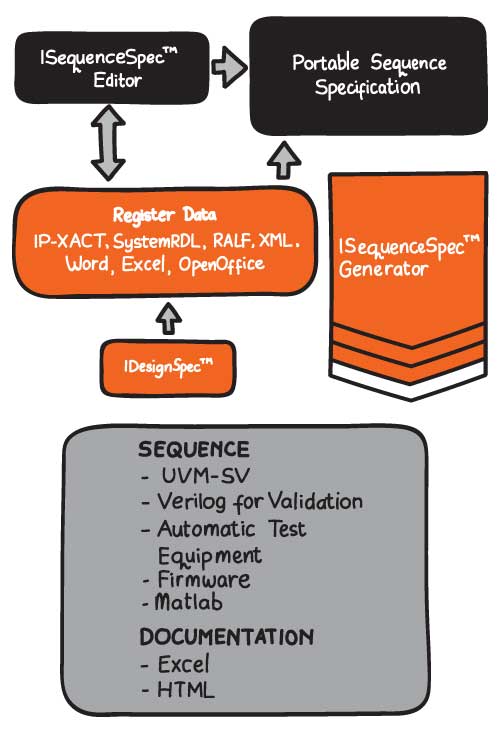

The basic tool flow of ISequenceSpec is shown in Figure 2. Multiple output formats such as UVM-SystemVerilog, C, Matlab, ASCI or CSV can be generated to implement the same stimulus that can be used for various stages of SoC development.

The tool idea for ISequenceSpec is a product of experience and mutual trust with our users. Our industry is never short of tool ideas, but as an EDA company we are always reminded that the success of a tool is not solely a function of its benefits, usefulness, ROI, differentiation, capital and team. Many great tool ideas simply fade out because they are too early or too late. The success of a tool is highly dependent on its timing within the industry. Being at the right time is a critical aspect of its adoption and success.

Our CEO and Founder has personally conducted a new on demand webinar to discuss the details of ISequenceSpec and how it can benefit your team. Go ahead and check it out – Generate Portable Sequences from a Golden Specification.