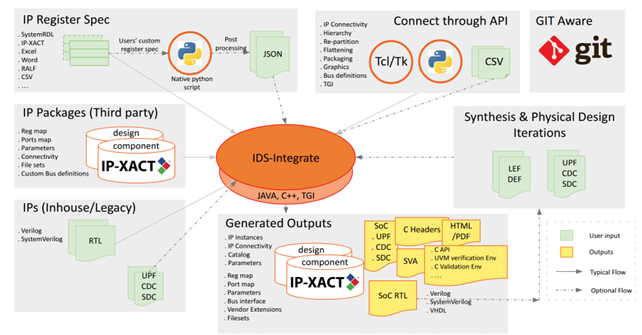

In this webinar, we will walk you through a comprehensive chip design automation flow that streamlines every stage—from capturing specifications, generating RTL, verification environments, firmware, and documentation, to enabling system-level validation. Learn how automation can reduce manual effort, eliminate inconsistencies, and accelerate design cycles while ensuring higher quality and compliance.

Key takeaways:

- Understand the challenges in today’s SoC/ASIC design process.

- Explore how an automated flow connects specs to RTL, UVM, firmware, and documentation.

- Discover the benefits of using automation for faster iterations and reduced errors.

eBook: How Agnisys Eliminates Redundancies in Semiconductor Design, Verification, and Validation

Overcoming the weaknesses of traditional natural language specifications requires writing the specifications in a precise format rather than natural language, and making this format executable so that tools can generate as many files as possible for the design, verification, programming, validation, and documentation teams. Such a solution is available today.

Recent Blog Articles

In today’s semiconductor industry, the most interesting and challenging chips are embedded SoCs. I think it’s worth mentioning that...

In my most recent blog post, I reminisced about childhood toys that let you construct complex structures from simple...

As kids, many engineers enjoyed toys that involved assembling complex designs from simple elements. Whether it was wooden blocks...