Leveraging SystemRDL for Efficient Register Modeling in Next-Gen SoCs

SystemRDL, or System Register Description Language, is a specialized hardware description language (HDL) used for specifying registers in digital systems. It is particularly common in the context of designing and documenting register maps for digital systems, such as microprocessors, field-programmable gate arrays (FPGAs), and other integrated circuits.

SystemRDL plays a crucial role in the design and delivery of intellectual property (IP) products. Its semantics are designed to support the entire life cycle of registers, encompassing specification, model generation, design verification, maintenance, and documentation. The scope of “registers” within this context goes beyond conventional configuration registers, extending to include register arrays and memories.

SystemRDL is crafted to enhance productivity, quality, and reusability in the intricate process of designing and developing complex digital systems. Its utility extends to the sharing of intellectual property (IP) among various entities, including groups, companies, and consortiums. The key mechanism involves specifying a singular source for the register description, enabling the automatic generation of various views. This approach guarantees consistency across multiple views, where a view encompasses any output derived from the SystemRDL description, such as register transfer level (RTL) code or documentation.

SystemRDL was developed to address challenges in describing and managing registers, especially in traditional environments. In the conventional approach, the system architect or hardware designer creates a functional specification for the registers in a design. This specification is often textual and lacks formal syntactic or semantic rules. Team members, including software, hardware, and design verification professionals, then use this specification to create representations of the data in the languages relevant to their roles in the chip development process. These languages may include Verilog, VHDL, C, C++, SystemVerilog/UVM, and others. Once the engineering team has an RTL implementation and verification infrastructure, the processes of design verification and software development can commence.

During the verification and validation processes, bugs are frequently identified, necessitating modifications to the original register specification. When such changes occur, all downstream views of this data must be updated accordingly, a process repeated multiple times during chip development. Additionally, there are two factors that can trigger alterations to the register specification. Firstly, shifts in marketing requirements may necessitate changes to a register’s specification. Secondly, physical considerations like area and timing constraints can drive modifications to the register’s specification. Challenges associated with this approach include:

- Replication of the same information across numerous locations and by various individuals

- Tedious, time-consuming, and error-prone propagation of changes to downstream users

- Postponement of documentation updates until late in the development cycle due to prioritization of more critical engineering tasks

These challenges frequently lead to a low-quality product and wasted time due to inconsistencies in register views. SystemRDL was specifically developed to address these issues by introducing a robust language capable of formally describing register specifications. By employing SystemRDL and a SystemRDL compiler, users can enhance efficiency and reduce errors by relying on a unified source of specification. This allows for the automatic generation of any required downstream views, eliminating the need for manual updates and ensuring consistency across the entire development process.

Key features of SystemRDL include:

- Register Description: SystemRDL allows designers to describe registers and their properties in a concise and human-readable format. All attributes of a register can be captured including the register width, fields inside it, and number of bits in each field, SystemRDL also has a capability of defining registers in two types of definitions: anonymous and definitive. In a definitive definition the register can be defined once and then used multiple times inside the specification with the help of instantiation.

SystemRDL Example:

Definitive Definition:

Anonymous Definition:

- Hierarchy: This supports hierarchical structures, enabling the description of complex register maps with nested modules and sub-registers.

| Component | Keyword | Description |

| Field | field | The field component is the lowest-level structural component, storing the bit information of a register |

| Register | reg | A register is defined as a set of one or more SystemRDL field instances that are atomically accessible by software at a given address |

| Register file | regfile | A register file is as a logical grouping of one or more register and register file instances |

| Address Map | addrmap | An address component map (addrmap) contains registers, register files, memories, and/or other address maps and assigns a virtual address or final address |

| Memory | mem | A memory is an array of storage consisting of a number of entries of a given bit width |

- Documentation: SystemRDL includes features for adding comments and documentation to the register description, making it easier for designers to understand the intended functionality.

- Parameterization: All the attributes of a component can be parameterized in the SystemRDL specification and the value can be changed later during instantiation of a component by parameter overriding.

SystemRDL Example:

reg myReg #(longint unsigned SIZE =32){ regwidth = SIZE; field { } data[SIZE – 1]; }; addrmap myAmap { myReg reg32; myReg reg32_arr[8]; myReg #(.SIZE(16)) reg16; myReg #(.SIZE(8)) reg8; };

In the above example, field bits and regwidth have been parameterized.

- Verification: The language includes constructs that facilitate the specification of properties for formal verification and documentation of intended behavior. Verification constructs like hdl_path, constraints, etc. can be specified in the SystemRDL specification.

SystemRDL Compiler Support:

Agnisys offers a SystemRDL compiler which can process SystemRDL files to generate documentation, perform verification checks, and even automatically generate synthesizable RTL code.

The compiler performs various semantic and syntax checks, encompassing all the checks and rules outlined in the SystemRDL standard, along with additional checks specified by Agnisys.

In addition to the features supported by the SystemRDL language, the Agnisys SystemRDL Compiler can interpret UDPs (User Defined Properties).It supports over 400 properties, enabling customization of the generated output and expanding the language’s capabilities.

For instance, while the native SystemRDL standard defines only alias, counter, and interrupt registers, the Agnisys SystemRDL Compiler, through the use of UDPs, can support a wider range of special registers. These include Lock, Alternate, Trigger-Buffer, Shadow, Indirect, FIFO, RO-WO Pair, Paged, Virtual, Multi-Dimensional, RegAlign, Wide, Triple Module Redundancy (TMR), and Accumulator, among others.

Advanced RTL features such as Clock Domain Crossing, Low Power RTL, Custom Circuitry, Parity/CRC/SECDED/Sniffer, Power/Performance Circuitry, Block Aggregation Logic, Security, and Power (Clock Gating) can also be achieved with the assistance of UDPs in SystemRDL.

Verification features such as coverage, customizing generated class names, and adding custom code in the generated UVM are among the capabilities supported by Agnisys, attainable in SystemRDL using UDPs.

SystemRDL Editor:

Agnisys also offers a SystemRDL editor within IDS-NG, which uses a text editor to open a SystemRDL file. It includes the following features:

- Basic Editor Features: The SystemRDL editor provides essential functionalities like copy, paste, select all, and find, enabling users to manipulate code swiftly and efficiently.

- Indentation: Clear and consistent code formatting is essential for readability and maintenance. The editor automatically handles indentation, ensuring that code remains organized and structured.

- Keyword and Syntax Highlighting: Critical keywords and syntax elements are highlighted, aiding developers in quickly identifying and understanding different components of SystemRDL code.

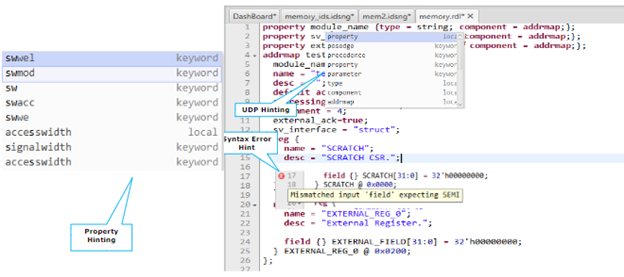

- RDL Property Hinting: The editor offers intelligent hinting for RDL properties, providing context-specific suggestions based on the applicable component, thus enhancing productivity and reducing errors.

- Template Hinting and Insertion: Template hinting assists users by suggesting relevant templates based on the applicable component, simplifying the process of code generation. Additionally, templates can be inserted with or without parameters, offering flexibility and customization options.

- RDL Syntax Error Highlights: Syntax errors are promptly identified and highlighted, allowing developers to rectify issues efficiently and maintain code integrity.

- Full Support for SystemRDL 2.0: The editor fully supports advanced features introduced in SystemRDL 2.0, including parameter overriding, dynamic assignment, and stride syntax (e.g., +=), empowering users to leverage the latest capabilities in their designs.

- Code Folding: Long and complex code segments can be collapsed or expanded, enabling users to focus on specific sections of code while decluttering the workspace.

- Error Reporting and Integration with IDS-NG: The editor seamlessly integrates with design tools like IDS-NG, providing real-time error checking and generation capabilities. Errors are pinpointed to specific line numbers, accompanied by standardized RDL messages, facilitating quick resolution and compliance with industry standards.

- Support for IDS UDP Properties: The editor extends support for IDS UDP properties, ensuring compatibility with a wide range of design components and enhancing design versatility.

- Usage Description and Documentation Links: Each property within the editor is accompanied by comprehensive usage descriptions and links to relevant documentation, empowering users with contextual information and resources for further exploration.