Agnisys | Next Generation of Register, Sequence, and SoC Automation

Regular readers of this blog know that Agnisys started as the first company to fully automate the design, verification, and documentation of registers in chip designs. From a single specification, you can generate design RTL, UVM testbench models for simulation, and user documentation for the registers in your design. This saves your development team weeks by swiftly propagating design changes across the project with a simple specification update and button push. IDesignSpec™ (IDS) remains our best-known and most widely adopted product.

We expanded our solutions to include the sequences to access and program your registers with IDS-Validate™ (ISS). We automatically generate sequences for various types of register behavior, including access to individual fields within registers. This is highly valuable for your chip verification team. We aid driver and firmware developers by auto-generating C code for accessing and programming registers in both fabricated chips and hardware-software co-simulation. Like IDS, ISS also generates documentation in several formats.

We extended our UVM support with the Automatic Register Verification (ARV™) add-on to IDS. ARV generates a complete verification environment for automatically verifying all your addressable registers across all access types. We create the complete UVM testbench: bus agents, monitors, drivers, adaptors, predictors, sequencers and sequences, and the verification plan. This testbench leverages the UVM register models generated by IDS. ARV also generates C code for driver development, interfaces with Portable Stimulus Standard (PSS) models, and supports formal verification.

Most recently, we have added much more support for system-on-chip (SoC) design and verification. At the recent virtual Design Automation Conference (DAC), we announced SoC Enterprise™ (SoC-E), and the Standard Library of IP Generators (SLIP-G™). SoC-E gives you the technology to assemble a complete SoC design, integrating SLIP-G components, other forms of external IP, and your design blocks. For standard buses such as AHB and APB, we generate RTL aggregators, bridges, and multiplexors as needed to meet the specified architecture for your SoC.

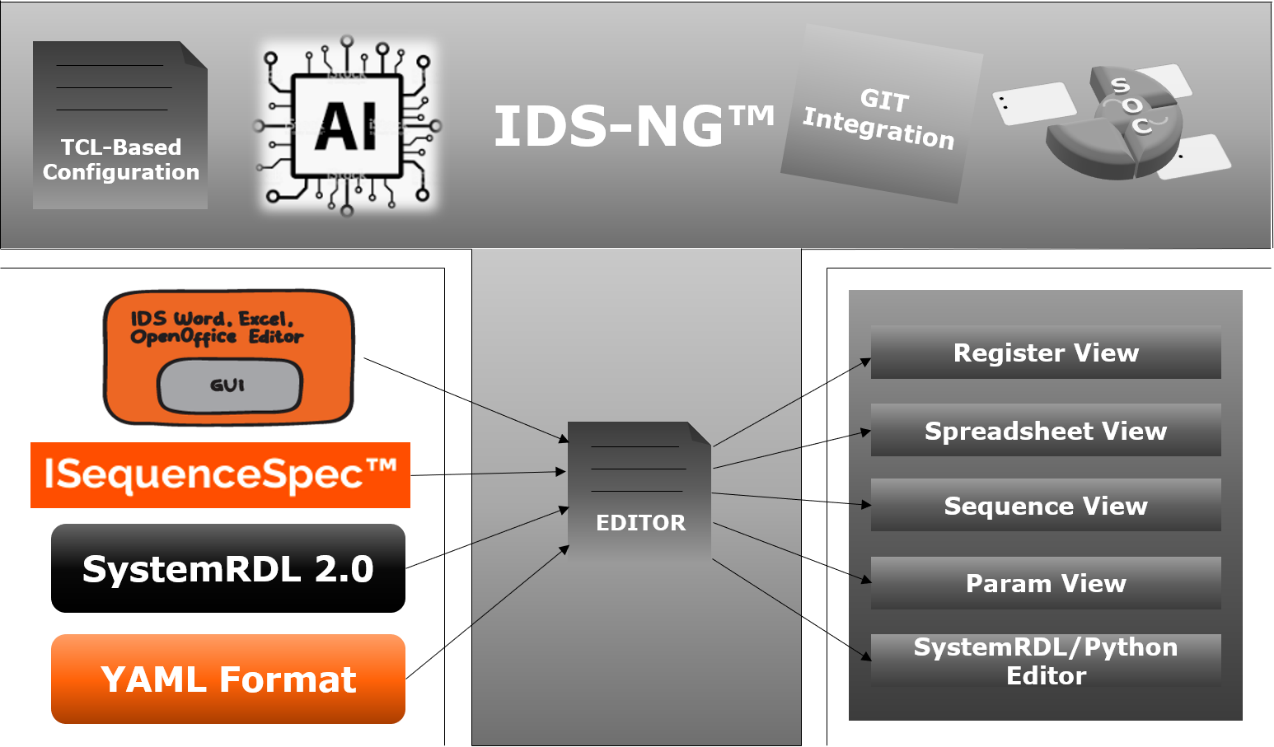

With this background as context, I’d like to discuss the third product we announced at DAC, IDS NextGen™ (IDS-NG). In many ways, it ties together key aspects of our complete product line. IDS-NG is a specialized integrated development environment (IDE) for large IP blocks and SoCs. It includes a sophisticated GUI for capturing register and sequence specifications. It provides a common front end for IDS, ISS, ARV, and SoC-E. IDS-NG enables a fully automated design and verification flow for registers and sequences.

IDS-NG supports a broad array of formats for input. It accepts register and sequence specifications created using Microsoft Word, Microsoft Excel, and OpenOffice plug-ins for IDS and ISS. It can import your existing register specifications in the SystemRDL or IP-XACT standard, Register Allocation Framework (RALF) format, or the YAML human-readable data serialization language. You can also use the sophisticated built-in IDE editor to create your register and sequence specifications within IDS-NG. With our IDE’s power and ease of use, we expect that many users will choose this option.

We provide numerous ways to view, review, and edit your specifications. For registers, we offer a domain-specific register view, a spreadsheet view for those who are used to Excel, a param view, and a SystemRDL editor. For sequences, we have a domain-specific view as well as a Python editor. Our integration with Git facilitates tracking, managing, and merging changes in your team’s specifications as they edit them, streamlining collaboration.

IDS-NG offers a huge range of output formats to support different users and different stages of your SoC project. For registers, these include:

- RTL design: Verilog/SystemVerilog, VHDL, and SystemC

- Verification models: UVM, OVM, VMM, eRM, and formal

- Headers for driver/firmware: C, C++, C#, Python, and Perl

- Documentation: HTML, PDF, Word, CSV, XML, and YAML

- Register standards: IP-XACT and SystemRDL

For sequences, IDS-NG can generate SystemVerilog or UVM for simulation, C for firmware verification, CSV for automatic test equipment (ATE) post-silicon validation, HTML for documentation, models for MATLAB analysis, and PSS models. There are additional output formats available now, and we are always open to adding more based on customer demand.

We regard IDS-NG as our new flagship product. It delivers on our longtime vision for a complete, fully automated, specification-based flow for registers and sequences from specification to assembly, design, verification, and validation of complex SoC devices. From a single specification, you can generate design RTL, complex programming and test sequences, UVM testbench models for simulation, PSS models, assertions for formal verification, C code for firmware and device driver development, CSV files for ATE, and user documentation in multiple formats.

Our solution enhances productivity, efficiency, and work quality for individual engineers and project teams while eliminating various system design and verification errors. Please view our recent webinar to learn more.