UVM REGISTER MODEL

UVM Register Model

The Universal Verification Methodology (UVM) standard defines the process of design verification for chips and intellectual property (IP). UVM testbenches and models are essential for many aspects of verification, and the standard has many features designed to help with specific tasks. One of these is the verification of the registers in the design.

UVM is Essential for Hardware Verification

Today’s huge and complex IP and system-on-chip (SoC) designs require thorough verification before chips are fabricated. Minimal testing by the designers and waiting until the chips are available in the bring-up lab is no longer an acceptable approach since chip turns are very expensive. Dedicated verification teams using the latest methods are required.

The SystemVerilog language provides the first part of the solution, with constructs that enable constrained-random verification and functional coverage to assess the efficacy of the automated tests. Because it is a standard, it is supported by many electronic design automation (EDA) tools and UVM verification environments are portable across EDA vendors.

The second part is UVM, a standardized verification methodology on top of SystemVerilog that provides building-block libraries and defines the structure of tests, models, and testbenches. Object-oriented techniques extend the standard set of base class libraries and methods for use across a wide range of projects, making advanced verification available to all teams.

Register Verification is a Requirement

IP and SoC designs contain many memory-mapped registers that are part of the hardware-software interface (HSI). They enable drivers and embedded software to configure and control the design while receiving back status. Ensuring that the registers in the register transfer level (RTL) design work as expected is a key part of pre-silicon verification.

As an example of register verification, the UVM tests might check that each register in the design can be read and written, perhaps applying “walking 0s” and “walking 1s” patterns. These tests can also check for intended behavior of specific register types, such as verifying that read-only registers cannot be written and that shadow registers always match.

UVM acknowledges the importance of register verification and includes specific support features. The standard includes the Register Abstraction Layer (RAL) for exactly this purpose. The UVM RAL provides a standard library of base classes and methods, along with a set of rules to minimize the effort to access registers from UVM testbenches.

UVM is Ideal for Register Verification

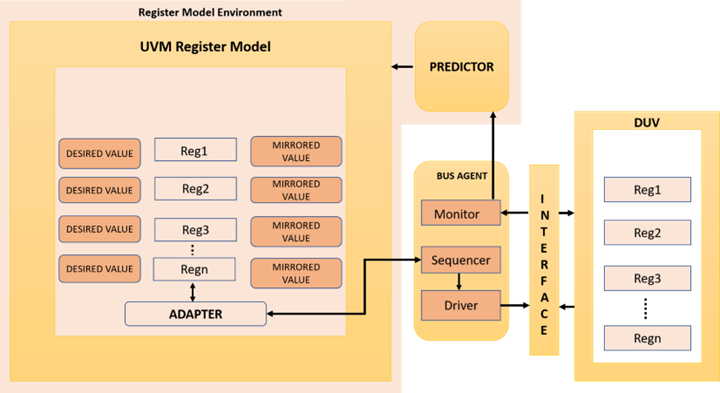

The RAL classes are used to create a high-level, object-oriented model for memory-mapped registers in the design under verification (DUV). The UVM RAL provides a high-level abstraction for reading and writing DUV registers using user-defined names. The registers can be accessed via the bus interface in the RTL design, or independently by calling read/write methods.

The UVM RAL provides a test sequence library containing predefined test cases that can be used to verify the DUV registers. As shown in the diagram above, these tests consist of complex sequences that apply stimulus directly to the DUV inputs. A monitor checks register contents at the end of tests to ensure that the values are equal to the predicted/expected results.

The UVM library register class does not include any built-in coverage model, but it provides an application programming interface (API) to control the instantiation and sampling of user-defined coverage models. This provides maximum flexibility for the verification team while acknowledging the importance of functional coverage in determining how well the tests have exercised the design.

Agnisys Provides the Best UVM RAL Solution

Agnisys IDS-Verify™ automates the generation of the UVM RAL verification environment, saving a huge amount of effort over hand coding and manual setup. The process starts with the definition of the registers in the design. IDS-Verify supports hierarchical register blocks, hierarchical register files, any number of registers, any number of fields within the registers, and any number of bits within the fields.

The Agnisys commitment to standards means that many ways of specifying the registers are supported. These include IP-XACT and register definition languages such as SystemRDL. For users who prefer graphical specification, Agnisys provides plug-ins to Microsoft Word, Microsoft Excel, and OpenOffice as well as a powerful register editor.

Register specification is a simple task of leveraging existing standard descriptions or filling out entries in a form. From a simple abstract input file, IDS-Verify produces complex SystemVerilog/UVM code to define, instantiate, and verify the registers. It generates new classes to define the registers, extending the “uvm_reg” base class from the standard UVM library

IDS-Verify Goes Beyond Other Solutions

Given that UVM RAL is a standard, it is supported by many tools and vendors. However, no other solution is as broad or as powerful as IDS-Verify. There are hundreds of special register types used in SoC and IP designs today, including indirect, indexed, read-only/write-only, alias, lock, shadow, FIFO, buffer, interrupt, counter, paged, virtual, external, read/write pairs, and combinations of these.

IDS-Verify supports all these special types of registers, generating the specific tests needed for 100% verification coverage of each type. It also supports memories, generating new classes by extending the “uvm_mem” base class, instantiating them in the verification environment, and generating tests. Other unique UVM RAL features of IDS-Verify include:

- Support for multiple types of coverage models

- Support for cross-coverage, for example on two register fields

- Specification of custom coverage and constraints

- Generation of UVM callbacks for aliased registers

- Auto-mirroring to update the UVM register model when an RTL register is updated

- Optional registration of register and memory classes with the UVM “factory”

Agnisys Covers All the Bases

UVM is the widely accepted way to verify SoC and IP designs. Verifying the registers and memories in the design is one of the key aspects of this process. IP-Verify provides an unparalleled solution for UVM RAL automation, generating all files from standard descriptions. Every time that registers change as the design evolves, the UVM environment is regenerated at the push of a button.

IDS-Verify is just one component of the Agnisys IDesignSpec™ specification automation suite. Users can also generate C/C++ tests for register configuration and verification, hardware/software co-simulation environments, register documentation, and even the actual RTL register designs. There is simply no better solution for adding, verifying, programming, and validating IP and SoC registers.