IDS-IPGenTM

Specification Automation for Glue Logic Generator

A typical SoC contains hundreds or thousands of RTL blocks from a variety of sources. Many chip companies maintain in-house libraries for commonly used design structures and interfaces. In addition, nearly all SoC projects also license IP blocks from partner companies or commercial IP providers, especially for blocks that implement a standard function such as AES, DMA, GPIO, I2C, I2S, PIC, PWM, SPI, Timer, or UART.

Automatically Keep Your IP Blocks Synchronized with the Specification

Leveraging IP and reusing parts of previous designs can save your SoC project team a huge amount of time and effort. The downside of using fixed IP blocks is that you may not be able to get exactly what they want. It may be possible to modify and customize IP, but this incurs the risk of breaking the standard functionality. Agnisys IDS-IPGen solves this problem by automatically generating IP blocks from specifications that are highly configurable and customizable.

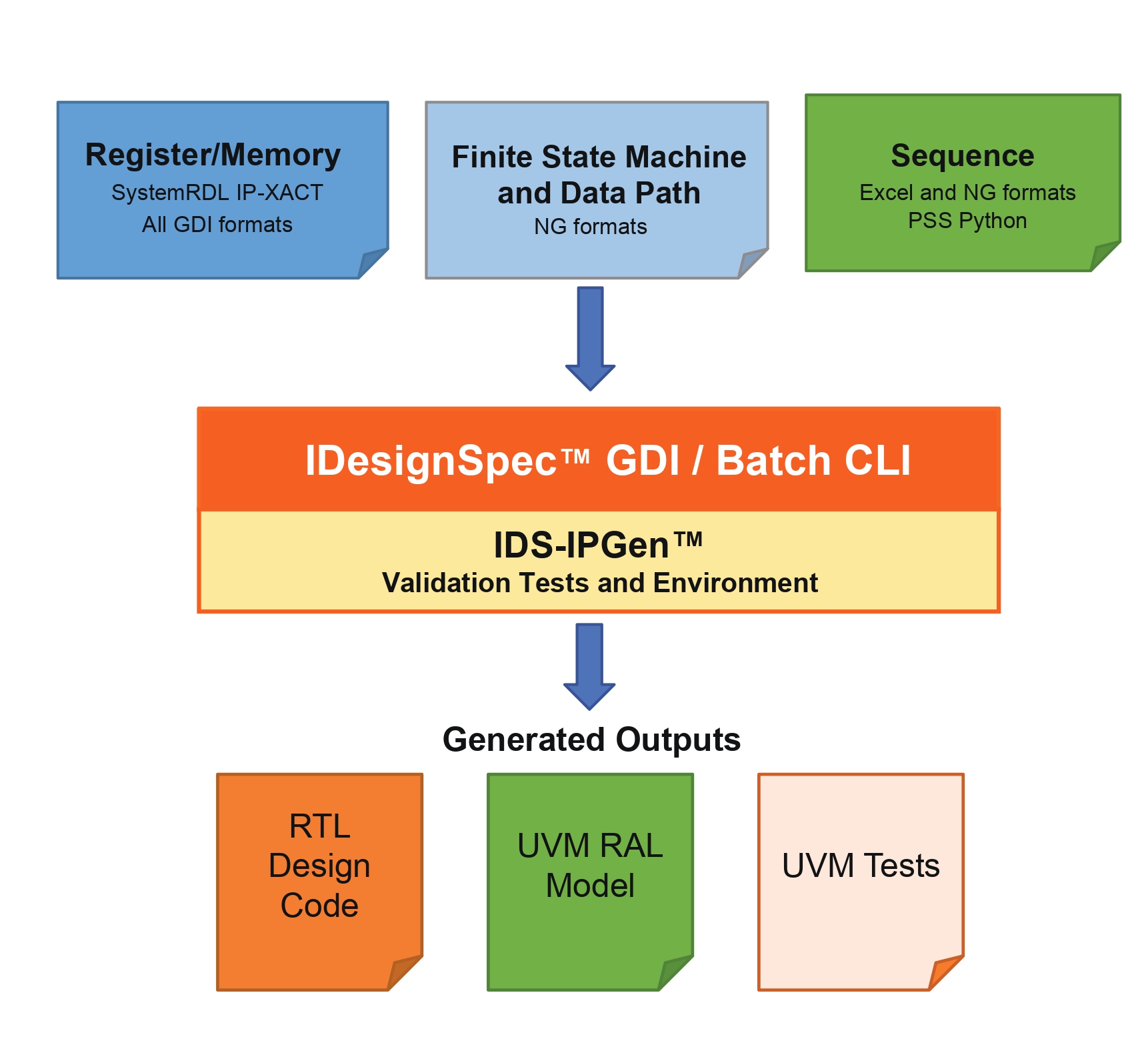

IDS-IPGen supports a wide variety of standard IP blocks as well as the specification of finite state machines (FSMs), data paths, signals, and other parts of your custom IP blocks. For both standard and custom blocks, IDS-IPGen generates RTL models, UVM verification models, and tests that provide high functional and code coverage right out-of-the-box.

More Details: Custom IP Design and AI-Based Verification

How IDS-IPGen Enhances Your Development Process

IDS-IPGen offers you the ability to choose many attributes of the IP design, including the options defined by any relevant standards. These may include bus widths, number of ports, optional functionality. The generator ensures that standards requirements are not compromised in the process of customization.

Flexible library of standard IP generators

By taking advantage of specification automation, IDS-IPGen generates many output files to benefit your project teams. It includes a powerful and flexible library of standard IP generators. Each library title generates a customized RTL design to meet your requirements.

Improves IP adoption

The RTL code reflects the customized aspects of the design, which you specify in the IDesignSpec GDI unified GUI. Some naysayers on using IP maintain that the verification and validation work for an unfamiliar design takes more time than just doing the design yourself. IDS-IPGen eliminates this objection because it handles all aspects of the IP block in every stage of development.

Download the IDesignSpec Suite Brochure

View a summary of each product and how the suite enables your semiconductor teams to more rapidly develop products while improving efficiency.

Benefits of IDS-IPGen

IDS-IPGen includes generators for numerous standard design blocks, including AES, DMA, GPIO, I2C, I2S, PIC, PWM, SPI, Timer, and UART. Your developers do not have to learn the many details of these complex protocols. For both standard and custom blocks, your designers do not have to manually develop the IP RTL code. Your verification engineers do not have to develop IP models or tests and do not have to struggle to meet coverage goals. This saves enormous time and resources on your project and moves verification and validation earlier in the schedule.

What Our Clients Say