New Product Advances Productivity for SystemVerilog UVM Verification

Agnisys just released DVInsight-Pro version 2.0 with many new features that enable much more productive SV/UVM code development.

Do you feel lost when you are facing UVM code? Do you have to sift through hundreds of files and use “grep” to search for lost classes or members? Do you get frustrated by seeing a large error dump only to find a silly typo in the code that would have been resolved quickly had the editor been smart? If so, consider using an editor that can catch UVM coding issues early in the development process when they are the least expensive to resolve.

Design and Verification Engineers can create correct by construction design verification code. DVInsight-Pro is a design verification editor and checker that provides valuable insight into user code and ensures compliance with UVM best practices while adhering to established industry standards and best practices. It helps new DV engineers to accelerate their learning curve while expediting error-free code development by the expert developer. The tool advances productivity for SystemVerilog Universal Verification Methodology projects. The new release significantly expands the tools capabilities.

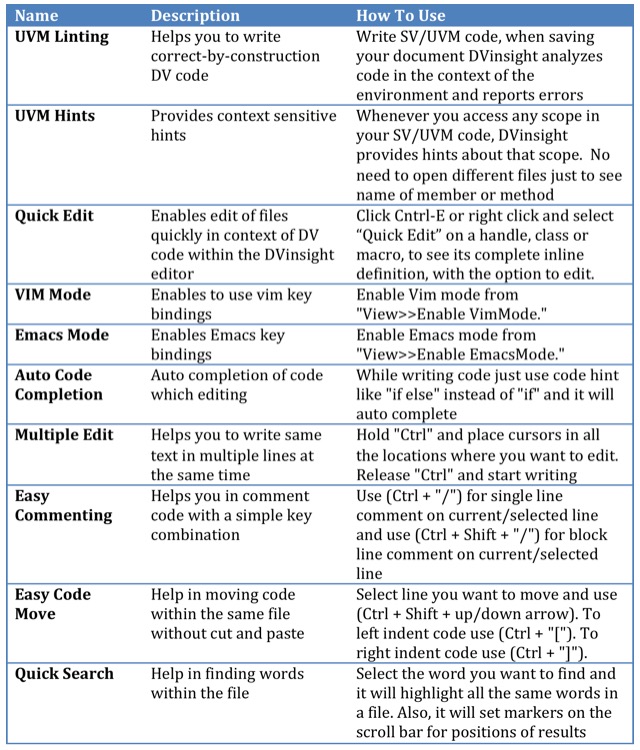

DVInsight-Pro has many new unique features: