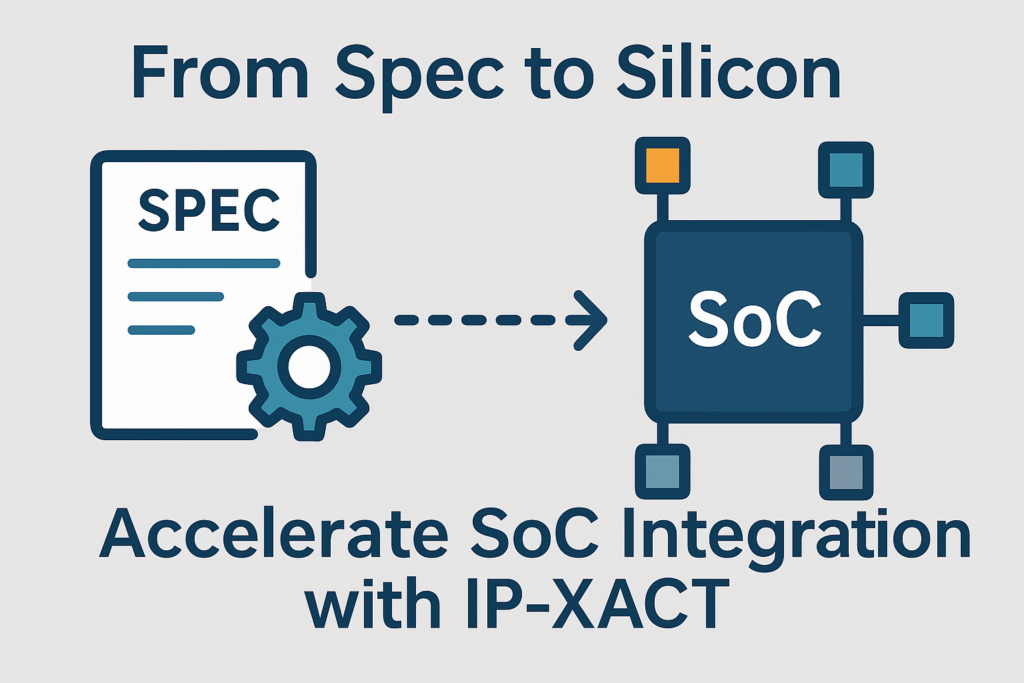

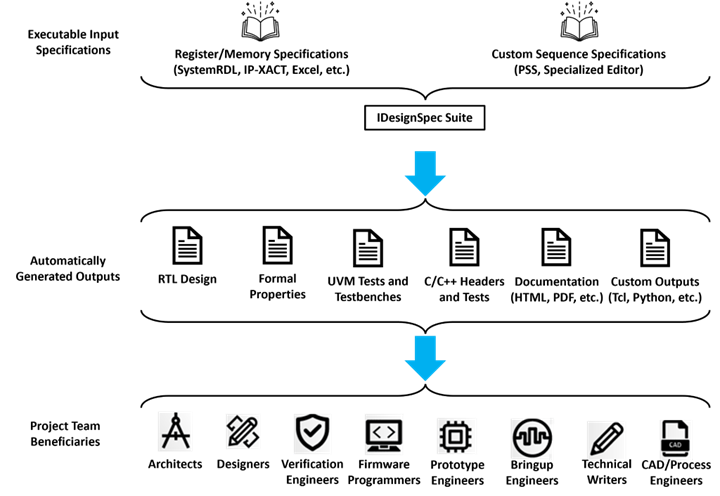

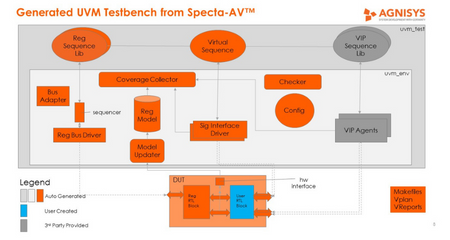

IDS-Verify™: From Specification to Sign-Off – Automated CSR, Hardware Software Interface and CPU-Peripheral Interface Verification

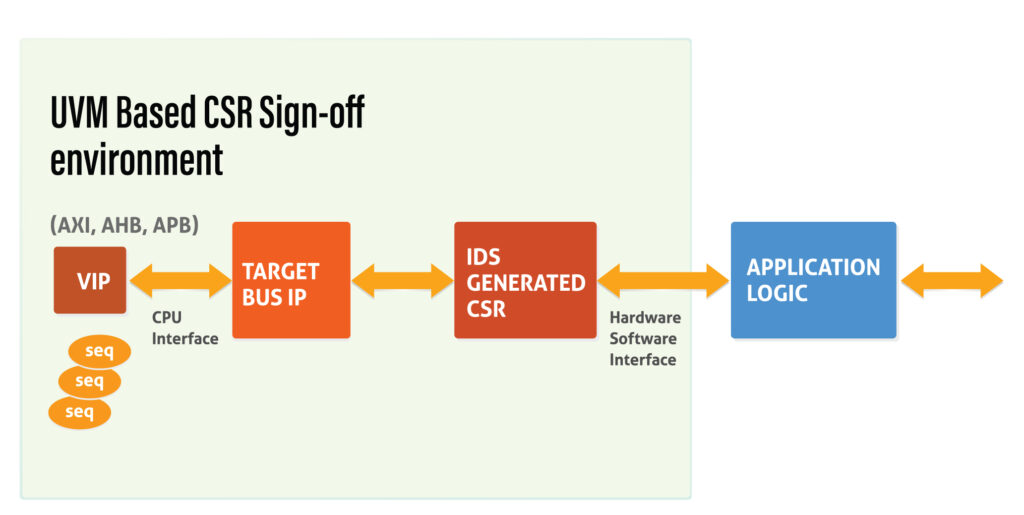

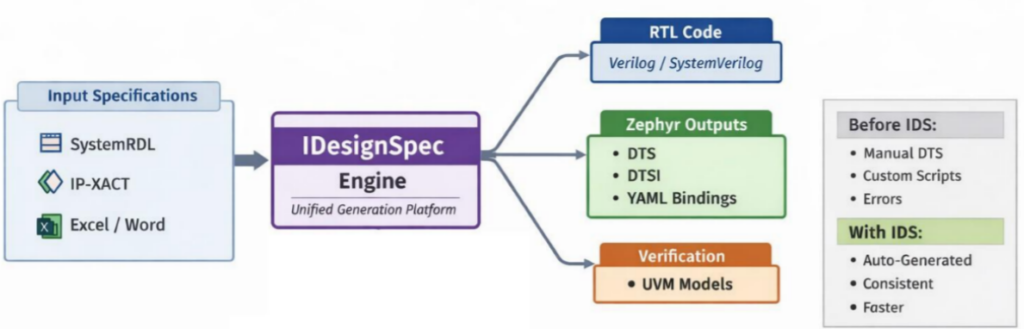

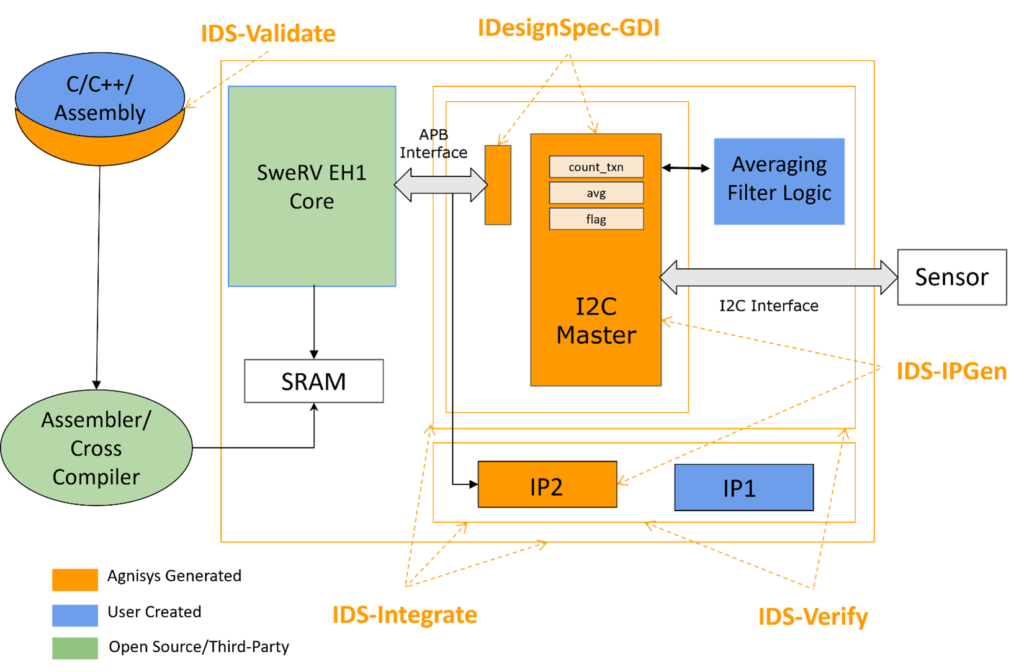

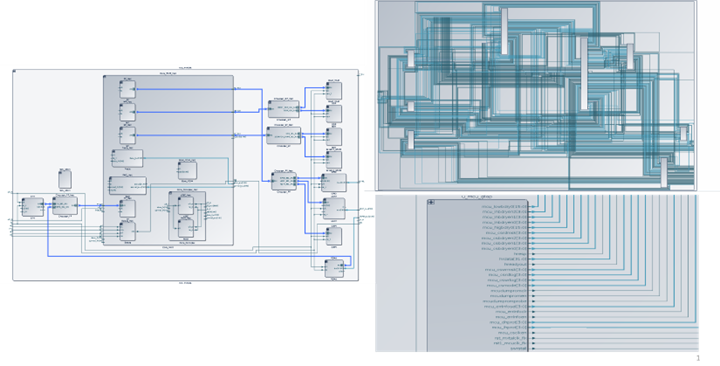

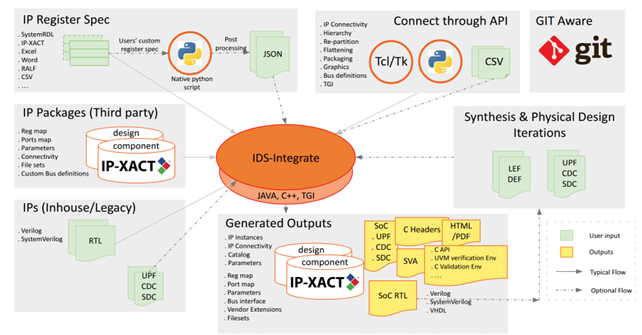

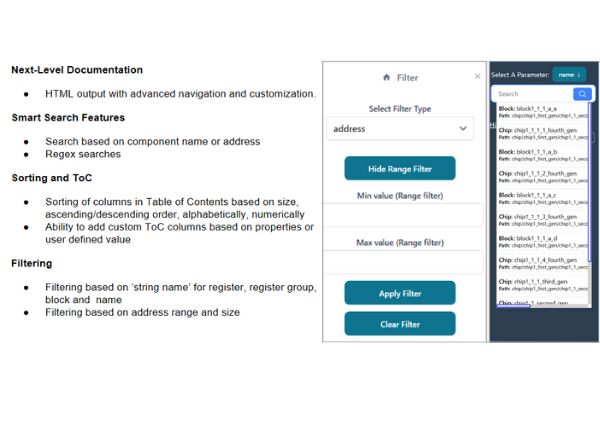

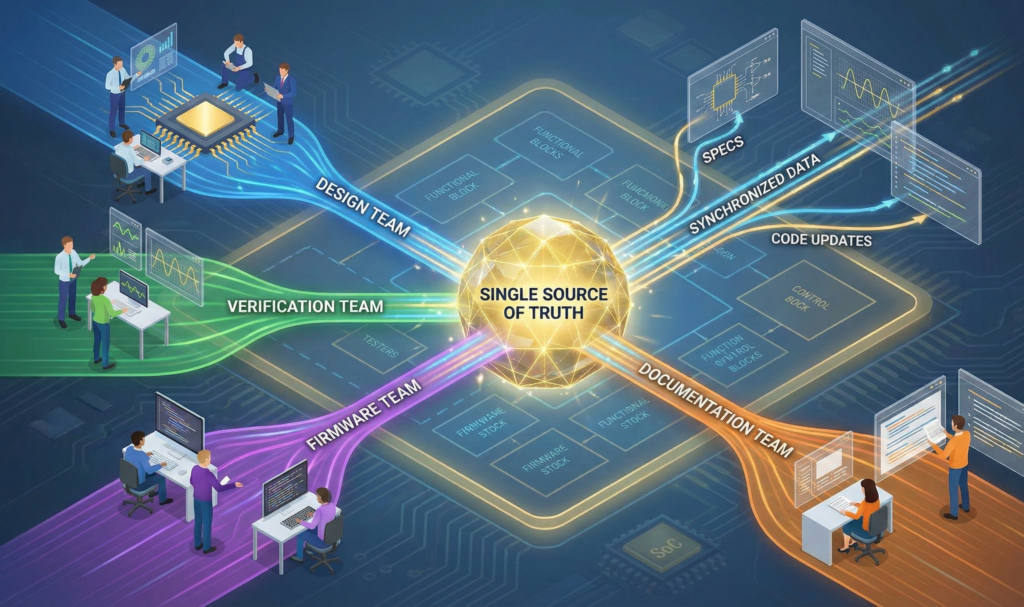

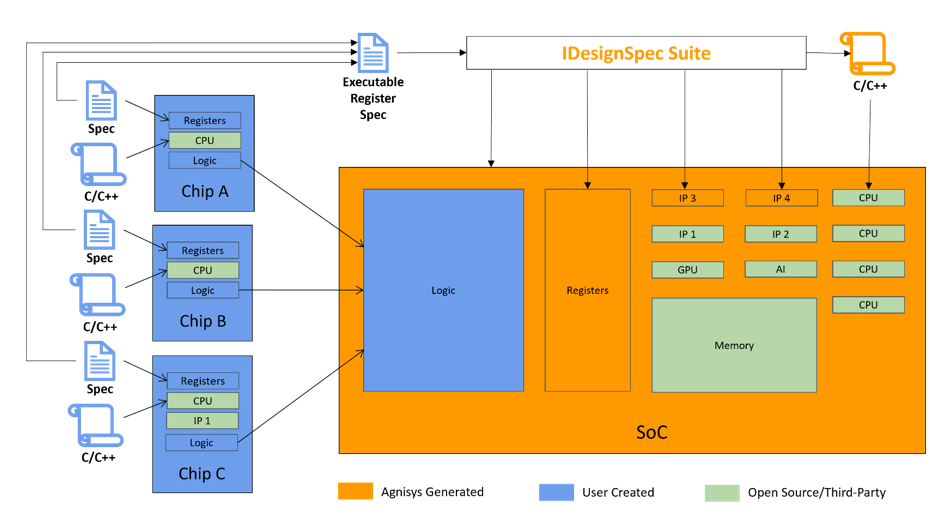

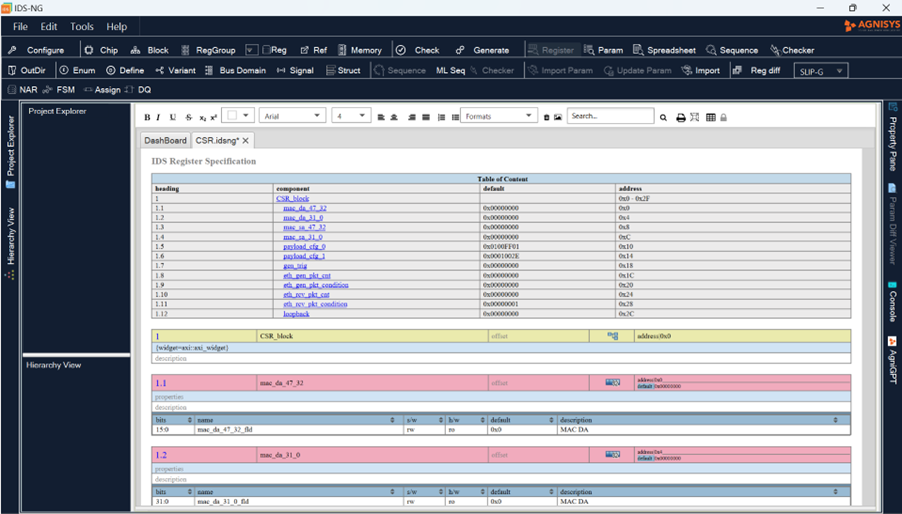

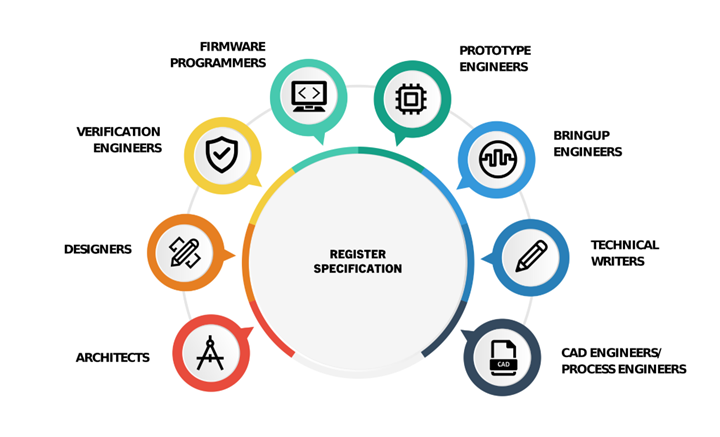

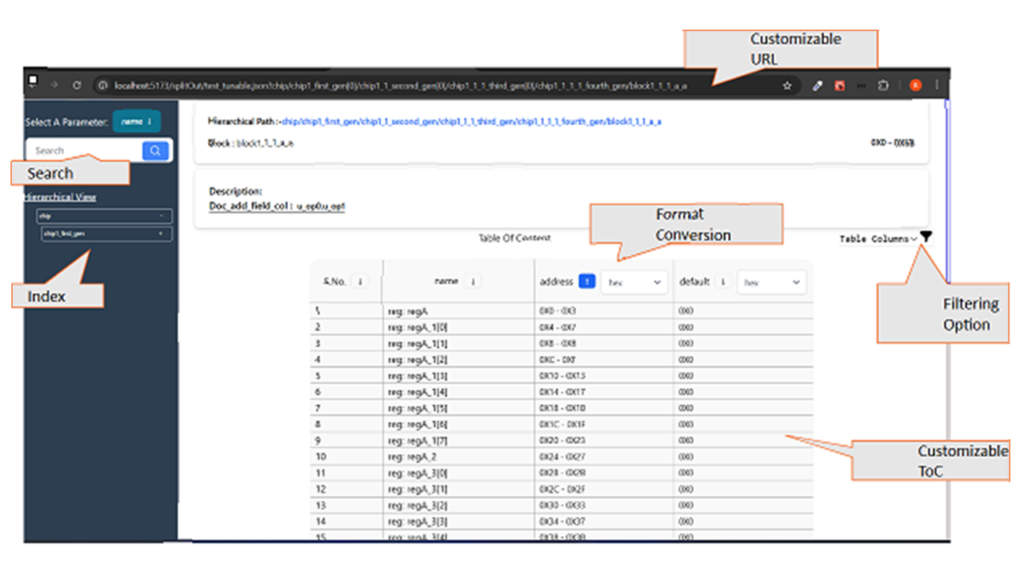

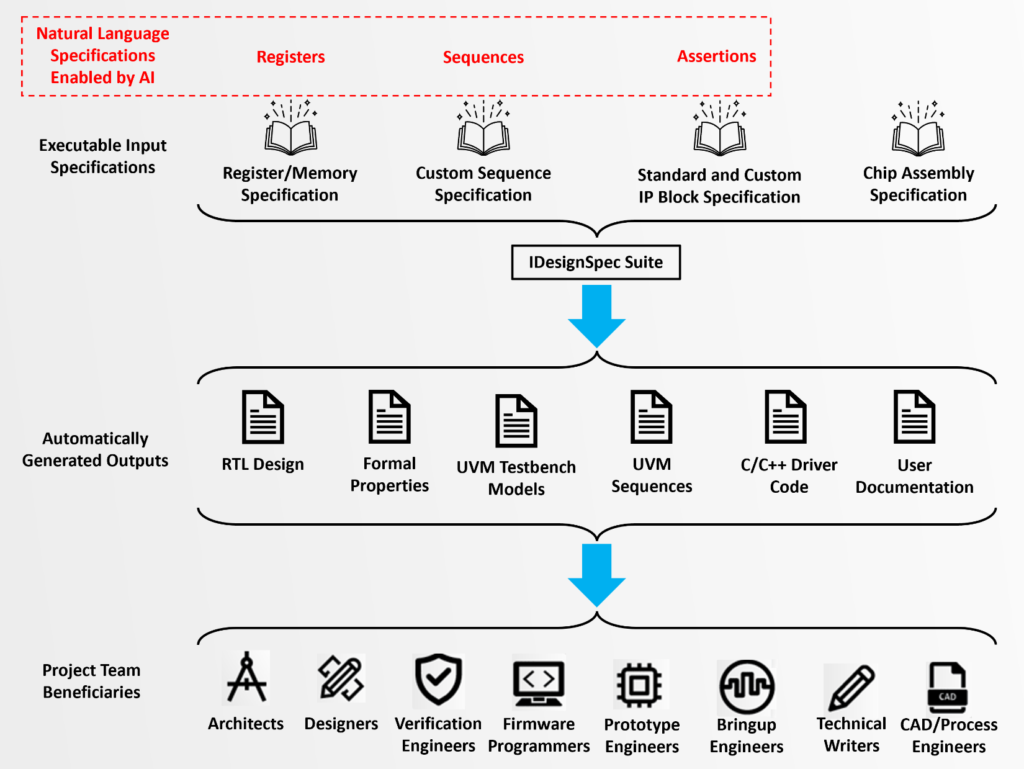

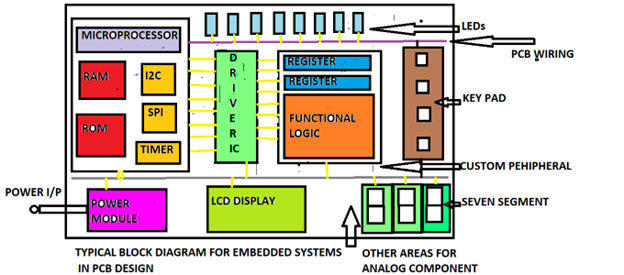

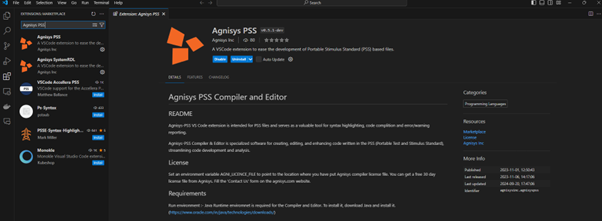

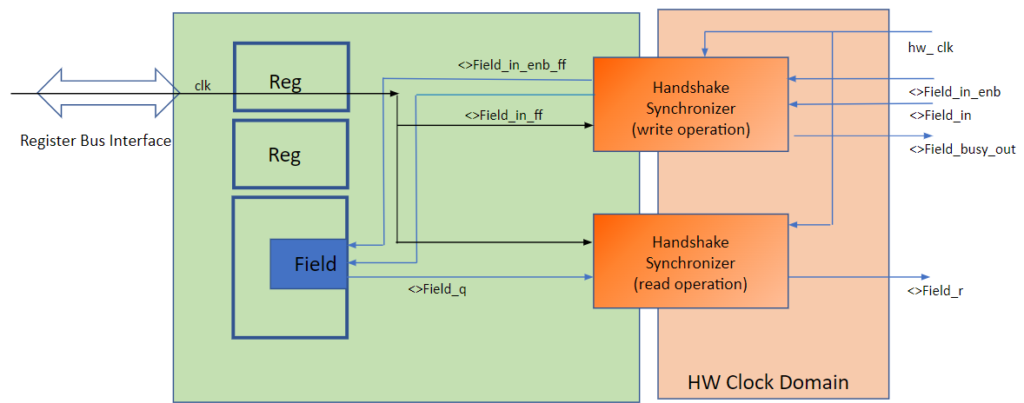

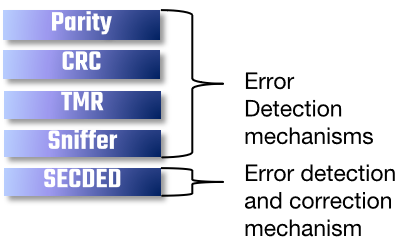

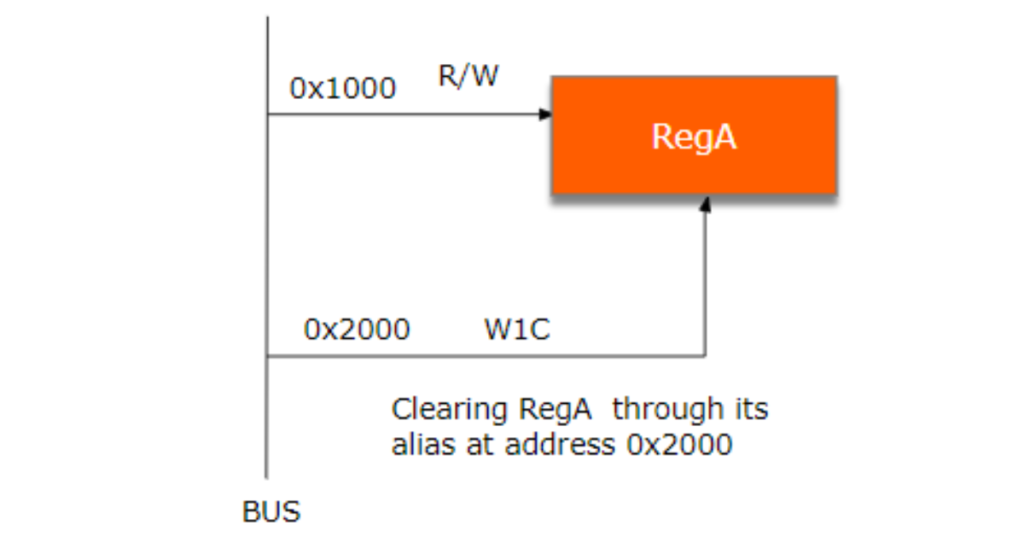

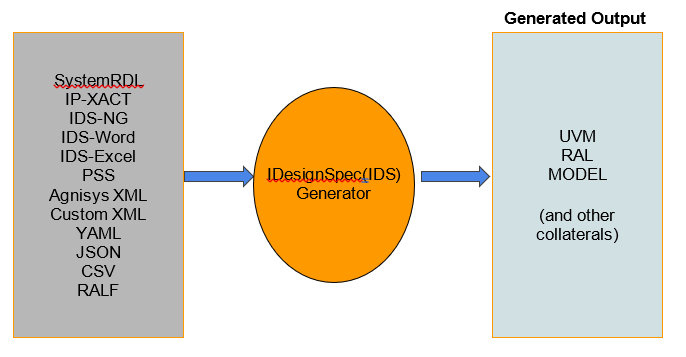

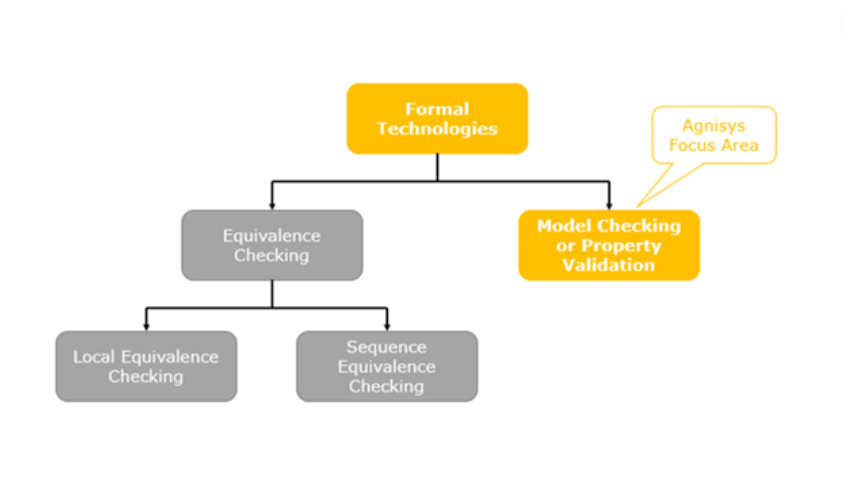

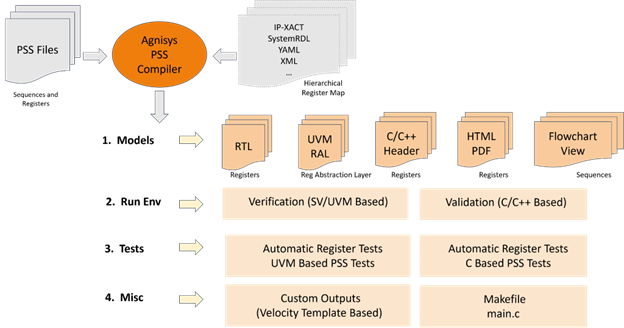

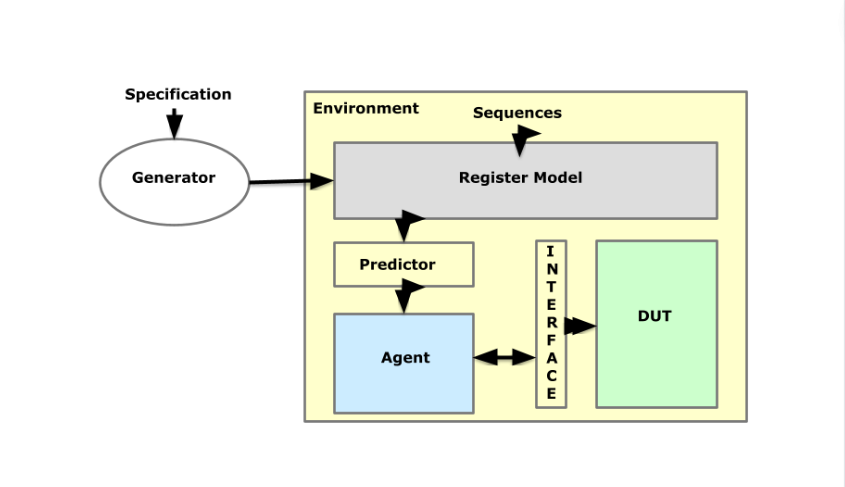

Verification of modern IP and SoC designs presents several challenges. Specifications are often interpreted differently across teams, such as design […]